### ECE 562

Week 6 Lecture 2

Fall 2008

### Week 6 Lecture 2 Summary

- Section notes

- Slides 3-4 Device sizes decrease over time

- Slides 5-15 MOSFET operation

- Slides 16-21— MOSFET characteristics

- Slides 22-31 MOSFET resistance

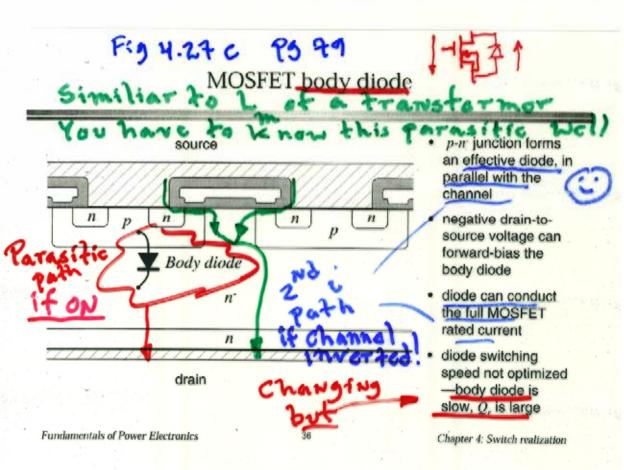

- Slides 32-34 MOSFET body diodes

- Slides 35-44 Reducing switch losses

- Slides 45-51 Commercial MOSFETs

- Slides 52-59 MOSFET parasitics and other non-ideal behaviors

- Slides 60-81 Efficiency and conclusion summary

# To date Summary of chapter 4

- How an SPST ideal switch can be realized using semiconductor devices depends on the polarity of the voltage which the devices must block in the off-state, and on the polarity of the current which the devices must conduct in the on-state.

- Single-quadrant SPST switches can be realized using a single transistor or a single diode, depending on the relative polarities of the off-state voltage and on-state current.

- Two-quadrant SPST switches can be realized using a transistor and diode, connected in series (bidirectional-voltage) or in anti-parallel (bidirectionalcurrent). Several four-quadrant schemes are also listed here.

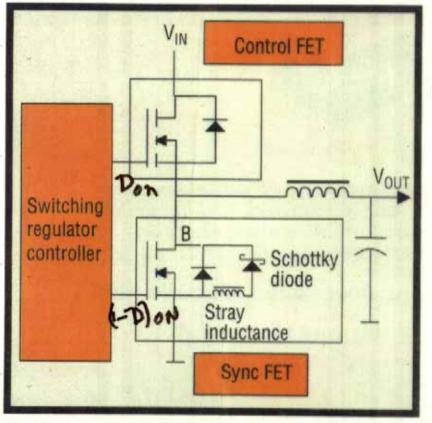

- 4. A "synchronous rectifier" is a MOSFET connected to conduct reverse current, with gate drive control as necessary. This device can be used where a diode would otherwise be required. If a MOSFET with sufficiently low R<sub>on</sub> is used, reduced conduction loss is obtained.

### 4.2. A brief survey of power semiconductor devices

- Power diodes

- . Power MOSFETS Tolay

- Bipolar Junction Transistors (BJTs)

- Insulated Gate Bipolar Transistors (IGBTs)

- Thyristors (SCR, GTO, MCT)

- On resistance vs. breakdown voltage vs. switching times

- Minority carrier and majority carrier devices

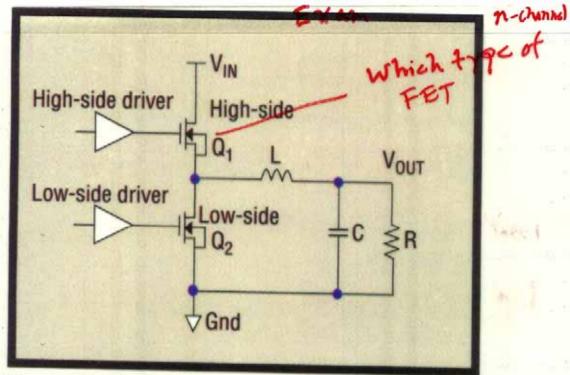

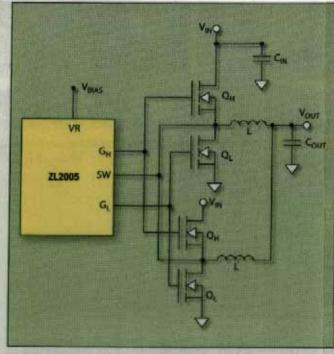

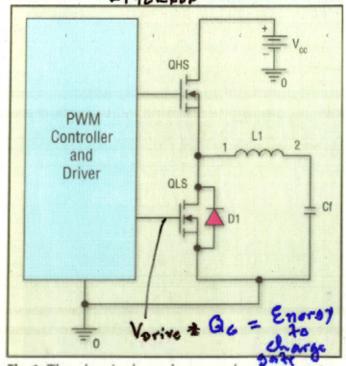

Fig. 1. Circuit diagram of dc-to-dc synchronous buck converter.

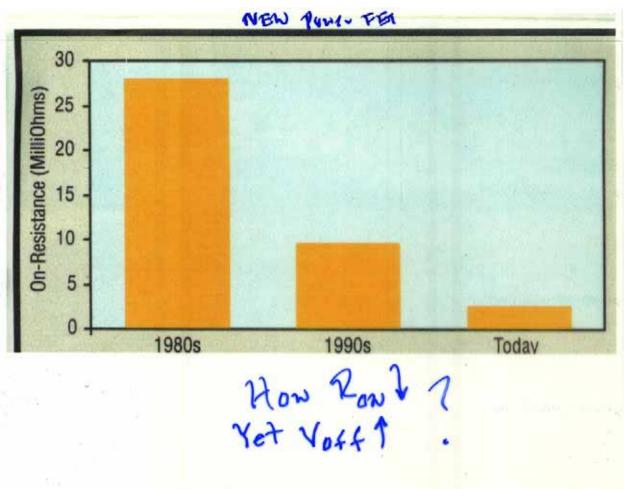

Ontimized M gated Trans

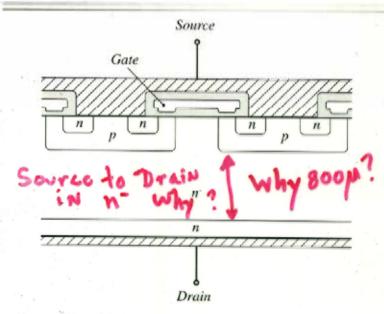

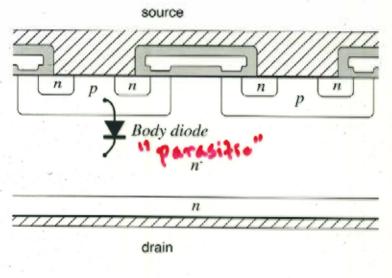

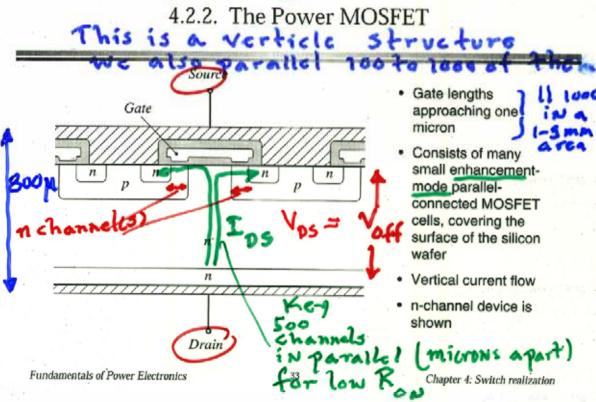

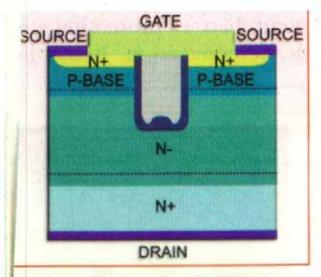

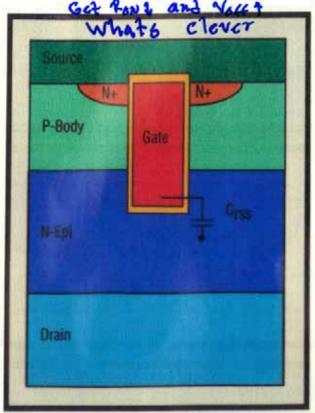

4.2.2. The Power MOSFET (Structure)

- Gate lengths approaching one micron

- Consists of many small enhancementmode parallelconnected MOSFET cells, covering the surface of the silicon wafer

- Vertical current flow

- n-channel device is shown

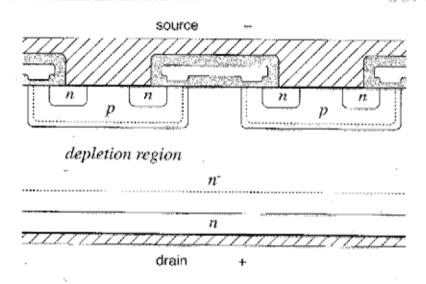

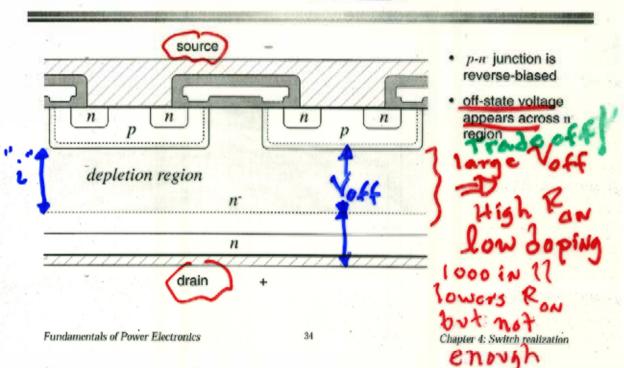

### MOSFET: Off state

p-n junction is reverse-biased

and the second of the contract of the second second

off-state voltage appears across negion

### Werkiek MOSFET: Off state

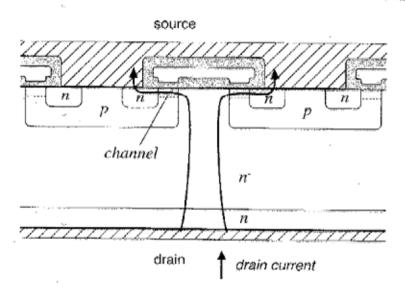

### MOSFET: on state

- p-n junction is slightly reversebiased

- positive gate voltage induces conducting channel

The state of the s

- drain current flows through n region and conducting channel

- on resistance = total resistances of n region, conducting channel, source and drain contacts, etc.

and the second of the second of the second

N. Administrative for the design of early become for a security and a security of the security

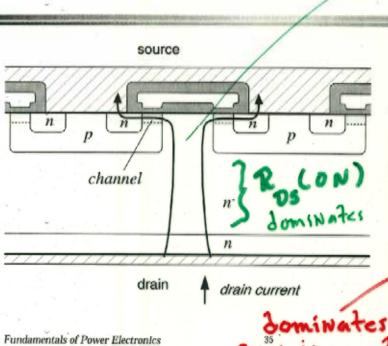

### Trerticle inversion channel

way to lower Rom

MOSFET: on state

- p-n<sup>-</sup> junction is slightly reversebiased

- positive gate voltage induces conducting channel

- drain current flows through n region and conducting channel

- on resistance = total resistances of n region, conducting channel, source and drain contacts, etc.

Chapter 4: Switch realization

## ZOV Direct FET 6628 D& Swloss high MOSFET PACKAGING

| Part #  | $R_{DS(on)} \ m\Omega$ @ 10 $V_{GS}$ | Q <sub>G</sub><br>(nC) | Q <sub>GD</sub><br>(nC) | Q <sub>sw</sub><br>(nC) | I <sub>o</sub> (A) | 11: |

|---------|--------------------------------------|------------------------|-------------------------|-------------------------|--------------------|-----|

| IRF6620 | 2.1                                  | 28                     | 8.8                     | 12                      | 150*               | 2"  |

| IRF6623 | 4.4                                  | 11                     | 4                       | 5.2                     | 55*                | 3 1 |

Table. Typical MOSFET specifications.

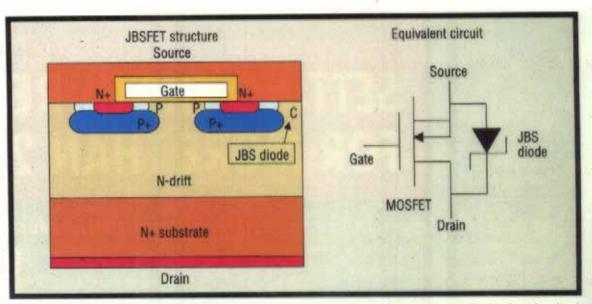

Fig. 5. JBSFET structure and its equivalent circuit with Junction Barrier controlled Schottky diode.

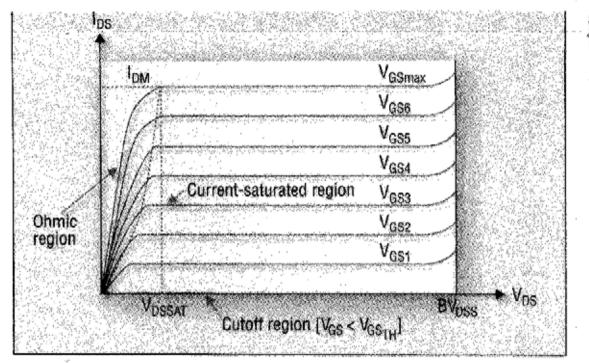

**Fig. 1.** As shown in this generalized graph of output characteristics, an n-channel power MOSFET has three possible modes of operation.

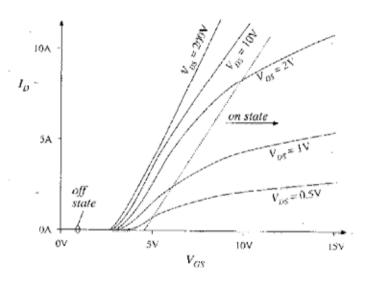

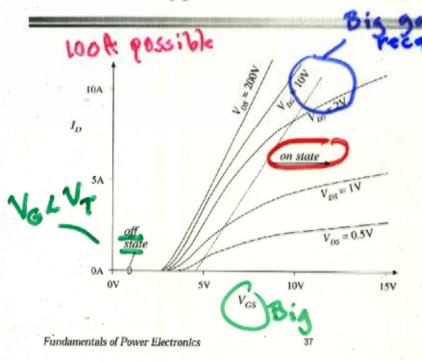

### Typical MOSFET characteristics

Off state: V<sub>GS</sub> < V<sub>th</sub>

and the second of the property of the second of the second

- On state:  $V_{GS} >> V_{th}$

- MOSFET can conduct peak currents well in excess of average current rating —characteristics are unchanged

- on-resistance has positive temperature coefficient, hence easy to parallel

Fig 4.28 79 80

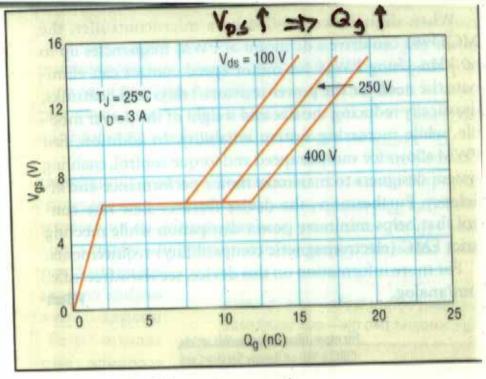

Cinto power Fet : 10nF

Typical MOSFET characteristics

- Off state: V<sub>GS</sub> < V<sub>ds</sub>

- On state: V<sub>GS</sub> >> V<sub>th</sub>

- MOSFET can conduct peak currents well in excess of average current rating characteristics are unchanged

- on-resistance has positive temperature coefficient, hence easy to parallel

Chapter 4: Switch realization

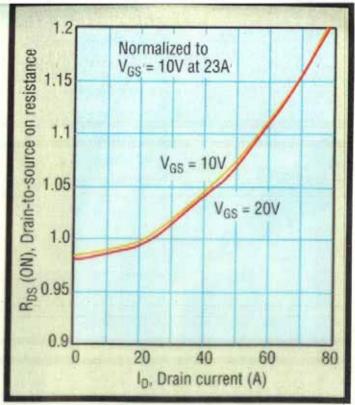

Fig. 3. Normalized R<sub>DS(on)</sub> for APT5010B2LL at

### Characteristics of several commercial power MOSFETs

| Part number | Rațed max voltage | Reted avg current | R <sub>os</sub> | $Q_{\varepsilon}$ (typical) |

|-------------|-------------------|-------------------|-----------------|-----------------------------|

| IRFZ48      | 60V               | 50A               | $0.018\Omega$   | 110nC                       |

| IRF510      | 100V              | 5.6A              | 0.5463          | 8.3nC                       |

| IRF540      | 100V              | 28A               | 0.077₽          | 72aC                        |

| APT10M25BNR | 100V              | 75A               | 0.025₽          | 171.nC                      |

| IRF740      | 400V              | 10A               | $0.55\Omega$    | 63aC                        |

| MTM15N40E   | 400V              | 1.5A              | 0.3Ω            | 110aC                       |

| APT5025BN   | 500V              | 23A               | 0.25Ω           | 83nC                        |

| APT1001RBNR | 1000V             | 11A               | 1.0Ω            | 150nC                       |

$x_1 \in A$  . By  $A_1 = A_2$  , we have  $A_2 = A_3$  , where  $A_3 = A_4$  , and  $A_4 = A_4$  , where  $A_4 = A_4$  , we have  $A_4 = A_4$  , where  $A_4 = A_4$

The second of the

95 81

### Characteristics of several commercial power MOSFETs

|             |                   |                   | IC > 10ml    | 48 SW                    |

|-------------|-------------------|-------------------|--------------|--------------------------|

| Part number | Rated max voltage | Rated avg current | Rou          | Q <sub>s</sub> (typical) |

| IRFZ48      | 60V               | 50A               | 0.018Ω       | 110nC                    |

| IRF510      | 100V              | 5.6A              | $0.54\Omega$ | 8.3nC                    |

| IRF540      | 100V              | 28A               | 0.077Ω       | 72nC                     |

| APT10M25BNR | 100V              | 75A               | 0.025Ω       | 171nC                    |

| IRF740      | 400V              | 10A               | 0.55Ω        | 63nC                     |

| MTM15N40E   | 400V              | 15A               | 0.3Ω         | 110nC                    |

| APT5025BN   | 500V              | 23A               | 0.25Ω        | 83nC                     |

| APT1001RBNR | 1000V             | 11A               | 1.0Ω         | 150nC                    |

Will expand mos usage Rand low Rand

Gatech

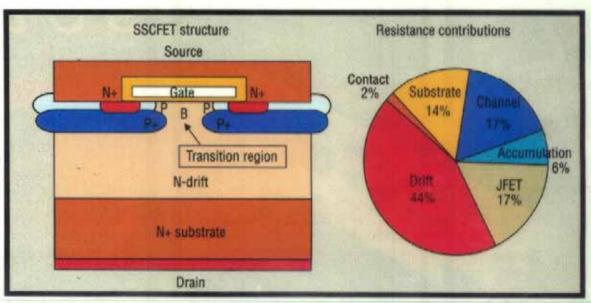

Fig. 4. SSCFET structure and its internal resistance distribution.

### dominates for HV Zevice

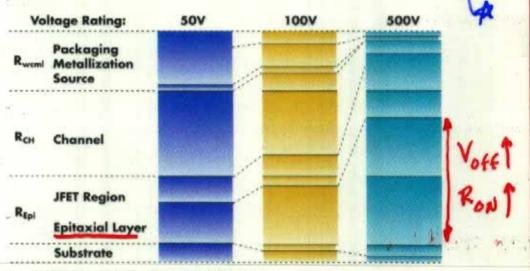

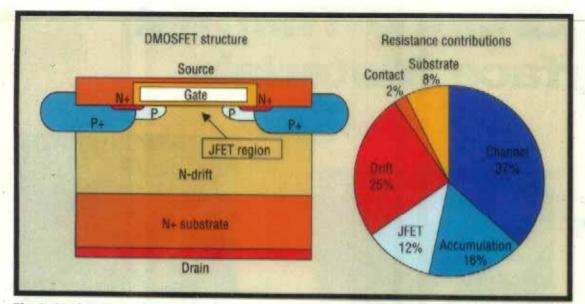

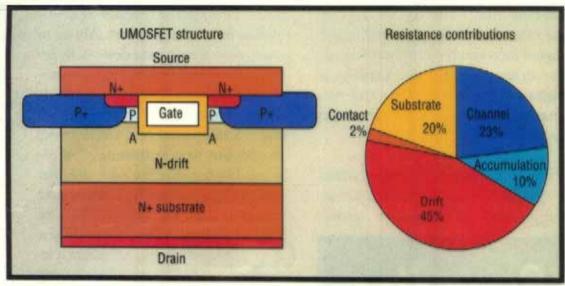

### ON-STATE RESISTANCE (RDS(on))

R<sub>DS(an)</sub> = R<sub>source</sub> + R<sub>ch</sub> + R<sub>A</sub> + R<sub>J</sub> + R<sub>D</sub> + R<sub>sub</sub> + R<sub>wcml</sub>

Substrate resistivity directly affects on-state resistance. For <u>high voltage devices</u> (500V) the total on-state resistance is dominated by Epi resistivity while for <u>low voltage devices</u> (50V) channel and external contacts and packaging play a more significant role. Substrate resistivity contributes more significantly to lower breakdown voltage devices.

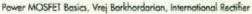

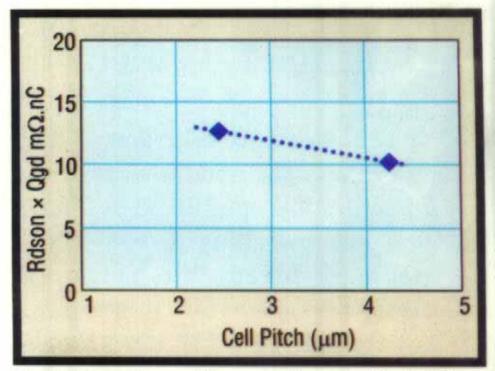

The MOSFET's figure of merit for on-resistance—the product of device resistance R and active die area—improves 30 percent with each new technology generation.

tataeo, asing

ed

t is

ent iet,

erthe

of her lease ow ve-

en

m-

ble

nal

or-

Fig. 1. A single-phase buck converter with dual inductors and dual MOSFETs on the high and low sides allow the use of standard low-profile components for a design that delivers 40 A. single-phase operation. This design will deliver 40 A, which

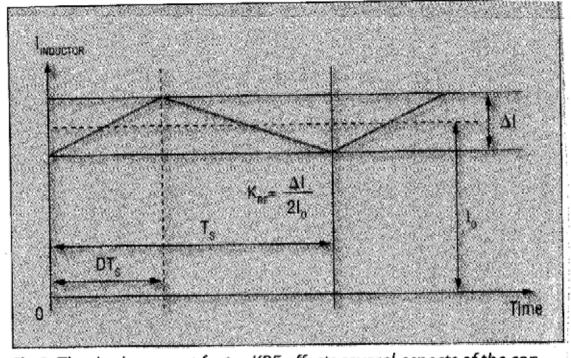

**Fig. 3.** The ripple-current factor KRF affects several aspects of the converter and must be established early in the design process. It is typically assigned a value between 0.1 and 0.2 <sup>[2]</sup>.

Pulse-width modulation: a control strategy for power converters, wherein the device is switched on and off with a duty cycle that keeps the average voltage over the switching period equal to the desired voltage value.

**Rectifier:** a power converter for acto-dc conversion, in which the power flows predominantly from the acto dc side.

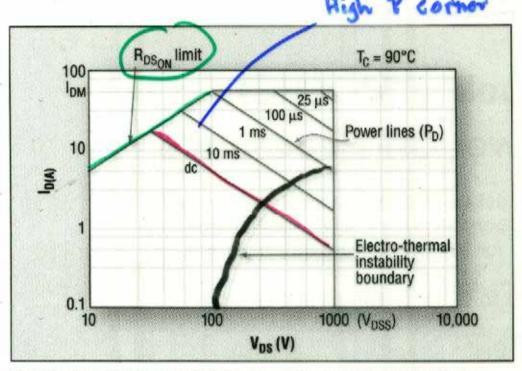

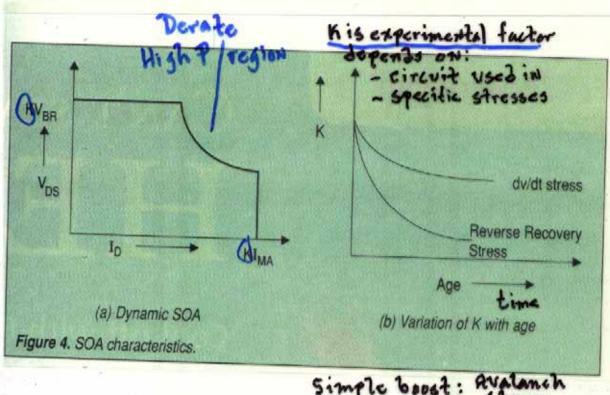

Safe operating area: a domain of voltage and current values within which the sustained operation of a device in various modes is safe. The modes include turn-on, turn-off, and on and off states.

**Fig. 2.** Power MOSFETs optimized for switched-mode designs have limited ability to operate in the corner of the FBSOA graph, where electro-thermal instability can occur as shown here for a typical n-channel power MOSFET.

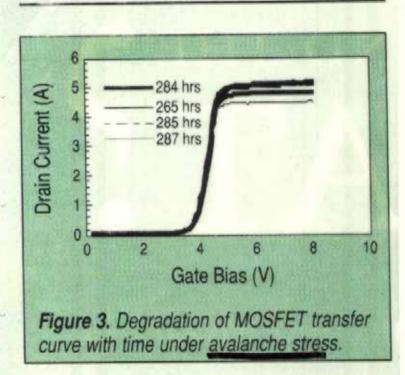

### SOA

With (stress) : Robocc Other Stress ceverse

TOLOVETY

Simple boost: Avalanch stress

Bridge: arrfrom body blade

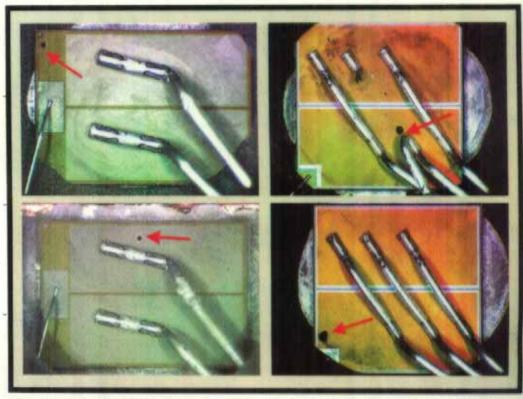

Fig. 3. Avalanche damage to Planar FETs (left) and Trench FETs (right). The bond-wire has been cut and moved out of the way to expose the damage in the part at upper right.

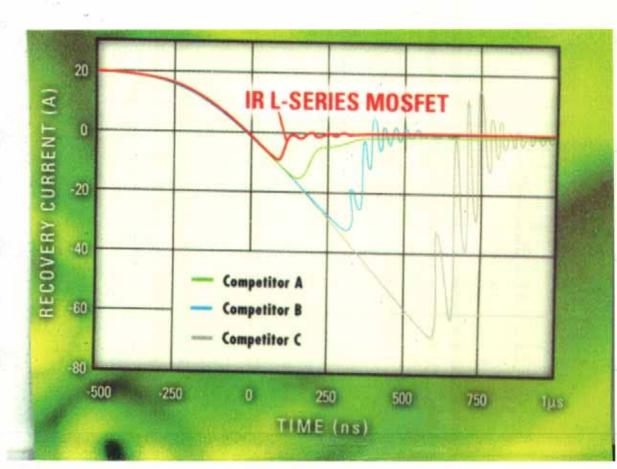

### MOSFET body diode

- p-n junction forms an effective diode, in parallel with the channel

- negative drain-tosource voltage can forward-bias the body diode

- diode can conduct the full MOSFET rated current

- diode switching speed not optimized —body diode is slow, Q, is large

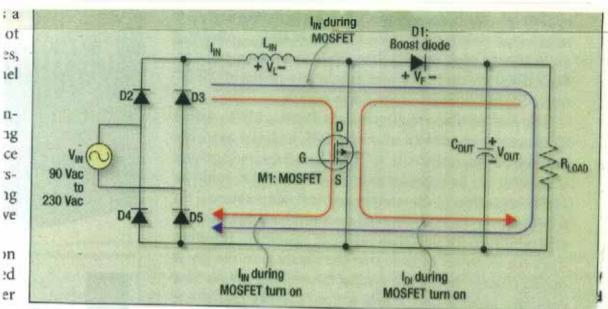

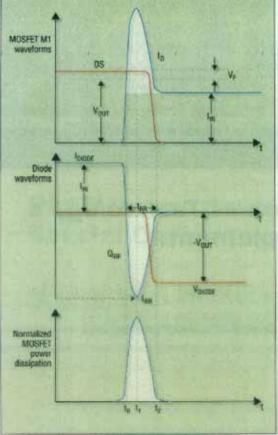

Fig. 1. In the basic PFC circuit operated in CCM, the reverse-recovery current of the boost diode significantly contributes to the switching losses of the MOSFET.

(N)

se

Fig. 2. The waveforms of a CCM PFC stage reveal how switching losses occur in pulses when non-zero valtages and currents, including reverse-secovery currents from the boost diode, overlap.

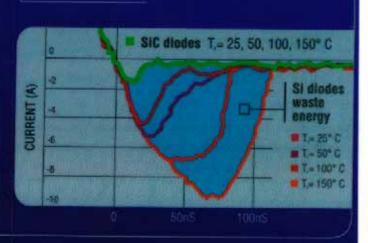

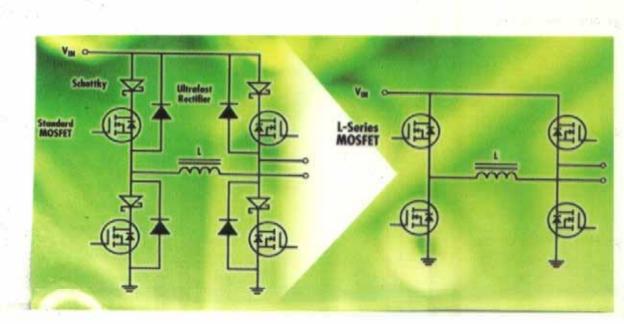

# SiC. THE MATERIAL OF CHOICE. ZERO RECOVERY Rectifier Higher frequency operation

Higher frequency operation

No high frequency ringing

Lower switching loss

Lower noise

Cooler operating temperature Higher power density

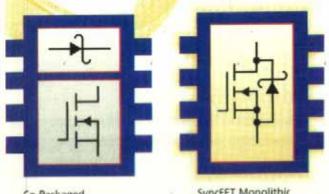

Co-Packaged MOSFET & Schottky

SyncFET Monolithic MOSFET & Schottky

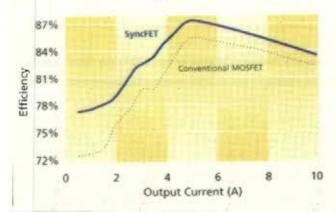

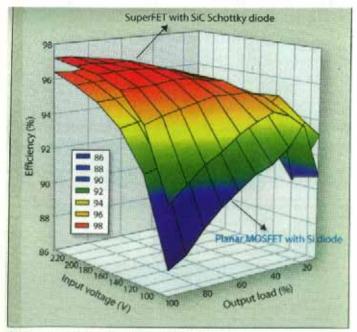

#### Effect of SyncFET on Efficiency

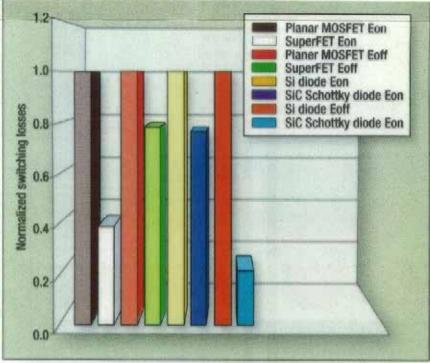

Fig. 5. The normalized switching losses of the SuperFET/SiC Schottky diode combination and the planar-MOSFET/Si diode combination reveal the substantial gains in efficiency provided by the former configuration.

Flg. 6. The efficiency of the SuperFET/SiC Schottky diode combination vs. the planar MOSFET/Si diode combination in a 400-W CCM PFC design directly translates into lower temperatures, higher power densities and reduced heatsink requirements.

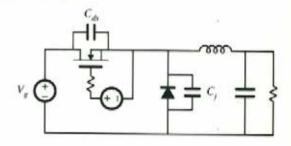

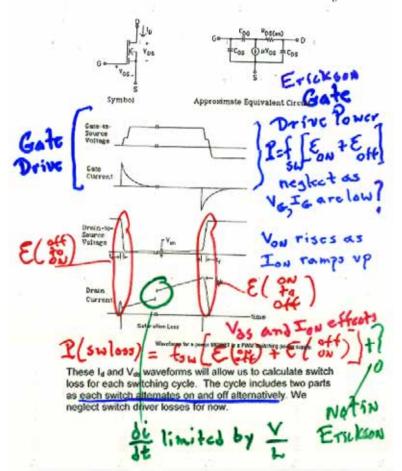

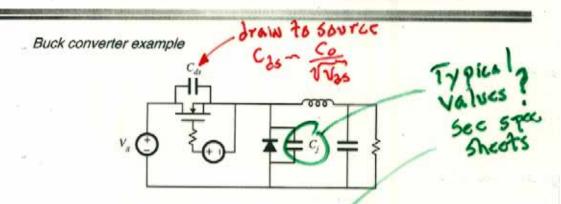

# Switching loss caused by semiconductor output capacitances

## Buck converter example

Energy lost during MOSFET turn-on transition (assuming linear capacitances):

$$W_C = \frac{1}{2} (C_{di} + C_j) V_g^2$$

### Some other sources of this type of switching loss

#### Schottky diode

· Essentially no stored charge

Significant reverse-biased junction capacitance

#### Transformer leakage inductance

Effective inductances in series with windings

A significant loss when windings are not tightly coupled

#### Interconnection and package inductances

- Diodes

- Transistors

- A significant loss in high current applications

Fig. 1. Sync-buck dc-dc converter topology.

|            | N SEC                | Control FET    |                                 | DATSW loss 7                 |                    |

|------------|----------------------|----------------|---------------------------------|------------------------------|--------------------|

| Туре       | V <sub>(BR)DSS</sub> | I <sub>D</sub> | R <sub>DS(on)</sub> max<br>@10V | Q <sub>g</sub> (tot)<br>@10V | Package            |

|            | [V]                  | [A]            | [mΩ]                            | [nC]                         |                    |

| STS12NH3LL | 30                   | 12             | 14*                             | 9.5*                         | 50-8               |

| STD38NHo2L | 20                   | 38             | 13.5                            | 18                           | <b>BPAK</b>        |

| STB50NH02L | 20                   | 50             | 13.5                            | 18                           | D <sup>2</sup> PAK |

| STD50NH02L | 20                   | 50             | 10                              | 22                           | DPAK               |

<sup>\*</sup>Available in Q1 2003. Values refer to 4.5V VGS

|             | Synchronous FET |                |                                           |                                      | £1      |

|-------------|-----------------|----------------|-------------------------------------------|--------------------------------------|---------|

| Туре        | (BR)DSS         | 1 <sub>0</sub> | $R_{DS(\alpha n)}$ max @10V [ $m\Omega$ ] | Q <sub>g</sub> (tot)<br>@10V<br>[nC] | Package |

|             | THE STATE OF    | No. Company    | 250000                                    | - Charles                            | DDAK    |

| STD90NH02L  |                 | 60             | 6                                         | 47-5                                 | DPAK    |

| STD100NH02L |                 | 60             | 4.8                                       | 62                                   | DPAK    |

| STB130NHo2L | . 20            | 90             | 4.4                                       | 69                                   | D2PAK   |

| STS25NH3LL  | 30              | 25             | 3.5                                       | 50                                   | 50-8    |

| STD150NHo2l | 20              | 150            | 3.3                                       | 69                                   | ClipPAK |

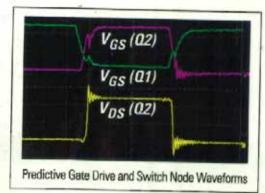

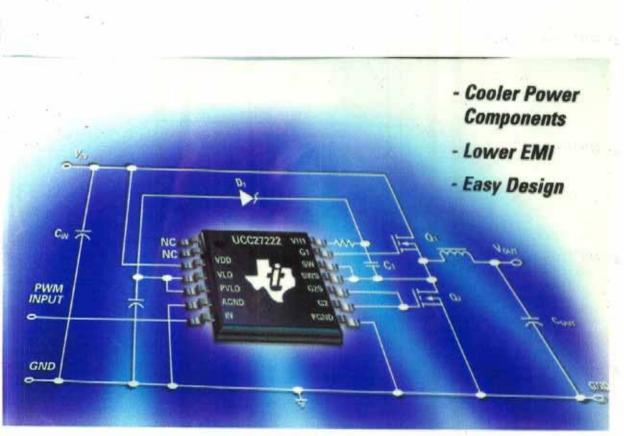

Texas Instruments introduces a new synchronous buck driver for today's low output voltage, nonisolated high-efficiency power converters. The **UCC27222** employs Predictive Gate Drive™ technology, which is a self-contained feedback system that looks ahead and optimizes the overlap of the two gate drive transitions. Adjusting for changing operating conditions, the Predictive

Gate Drive minimizes body diode conduction and reverse recovery losses for up to 4% efficiency gain over adaptive drive technologies and up to 40% improved thermal dissipation for higher reliability.

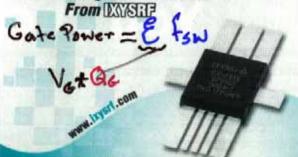

# **MOSFET Gate Drive ICs**

Introducing The New DEIC515

- Operation to greater than 28MHz

- 15A current output

- Kelvin inputs Higher frequency

- Lower operating currents

- Smaller size

- Performance optimized lead arrangement

- Lower propagation delay

#### Applications

- Class D and E RF Generators Acquistic Transducers

- · Laser Diode Drivers

- O HF PF Correction

- HF SMPS

- Pulse Generators

970-493-1901 . Informitys com

Typical Power FET Cg = lonf P~ 2 Cg Vg \* fsw = 10 10 if Cg - 10 pt P~ CgVg fow = 10 10 10 100W (2)

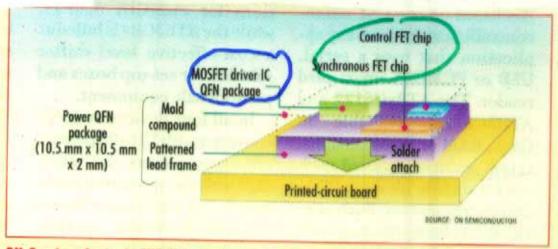

ON Semiconductor's NIS3001 implements the company's package-within-a-package technology, which typifies the arriving breed of power devices that extends the building-block multichip module approach to dc/dc converters.

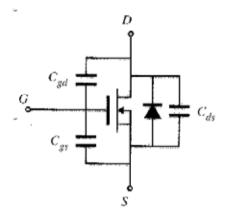

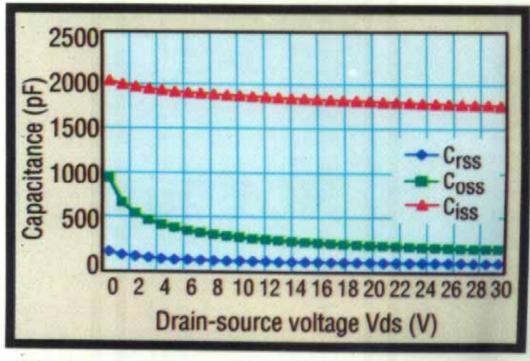

## A simple MOSFET equivalent circuit

$$C_{ab}(v_{ab}) = \frac{C_a}{\sqrt{1 + \frac{v_{ab}}{V_o}}}$$

- C<sub>s</sub>: large, essentially constant

- C<sub>gd</sub>: small, highly nonlinear

- C<sub>ds</sub>: intermediate in value, highly nonlinear

- switching times determined by rate at which gate driver charges/discharges C<sub>ga</sub> and C<sub>gd</sub>

$$C_{ii}(v_{\infty}) \approx C_0 \sqrt{\frac{V_0}{v_{ds}}} = \frac{C_0}{\sqrt{v_{ds}}}$$

from goods a recognition was a

# CV= Q Cast when Vast is good Il for fast off time on 11

## Fig 4.29 9580

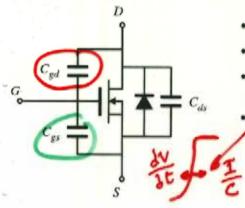

More free Parasitic elements: C

$$C_{ds}(v_{de}) = \frac{C_0}{\sqrt{1 + \frac{v_{ds}}{V_0}}}$$

- C<sub>gs</sub>: large, essentially constant

- · C<sub>sd</sub>: small, highly nonlinear MillerC

- C<sub>ds</sub>: intermediate in value, highly nonlinear

- switching times determined by rate at which gate driver charges/ discharges  $C_{gs}$  and  $C_{sd}$

$$C_{ds}(v_{ds}) \approx C_0 \sqrt{\frac{V_0}{v_{ds}}} = \frac{C_0}{\sqrt{v_{ds}}}$$

## MOSFET nonlinear $C_{ds}$

Approximate dependence of incremental  $C_{de}$  on  $v_{de}$ :

$$C_{ds}(v_{ds}) \approx C_0 \sqrt{\frac{V_0}{v_{ds}}} = \frac{C_0}{\sqrt{v_{ds}}}$$

Energy stored in  $C_{ds}$  at  $v_{ds} = V_{DS}$ ;

$$\begin{split} W_{Cds} &= \int v_{ds} \, i_C \, dt = \int_0^{v_{DS}} v_{ds} \, C_{ds}(v_{ds}) \, dv_{ds} \\ W_{Cds} &= \int_0^{v_{DS}} C_0(v_{ds}) \, \sqrt{v_{ds}} \, dv_{ds} = \frac{2}{3} \, C_{ds}(V_{DS}) \, V_{DS}^2 \end{split}$$

- same energy loss as linear capacitor having value  $\frac{4}{3}C_{\sigma}(V_{p_0})$

Fig. 8. Capacitances of a WFET vs. drain voltage.

Fig. 1. A typical MOSFET gate-charge graph.

Fig. 3. When a MOSFET switch is activated at zero V<sub>dd</sub> the Miller plateau goes away.

## Fig 4.52 Pg 98

Example: semiconductor output capacitances

Energy lost during MOSFET turn-on transition (assuming linear capacitances):

$$W_c = \frac{1}{2} (C_{ds} + C_s) V_s^2$$

R was off is Cas more or mil "eat" This during turn-on

Fundamentals of Power Electronics

Gate drive loss not covered by Etickson

Fig. 1. The classical synchronous buck converter uses two switching MOSFETs: the high-side (control) device, QHS, and the low-side 2 synchronous rectifier, QLS.

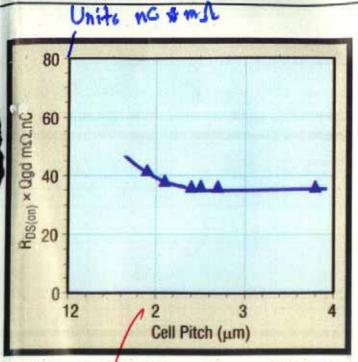

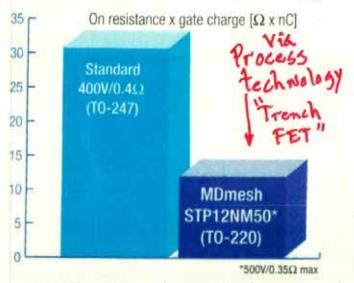

STMicroelectronics tweaks gate geometries and cell densities to improve figure of merit—the product of on-resistance and gate charge—in its StripFET III line.

Fig. 3. Figure of Merit R<sub>DS(an)</sub> ×Q<sub>gd</sub> vs. cell density of a conventional PWM Trench MOSFET.

Willexplain Soon

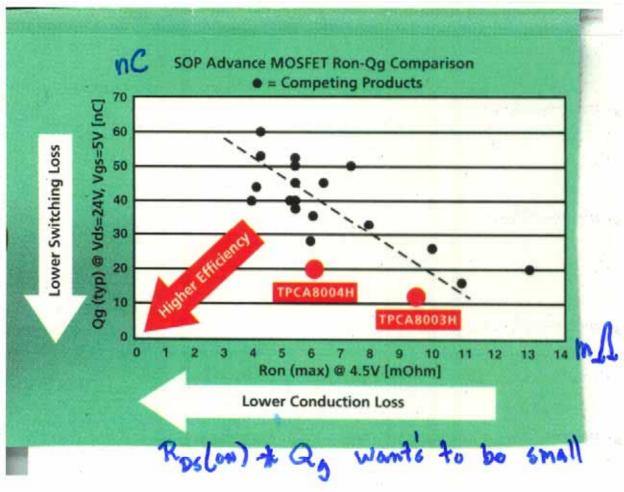

# MDmesh Cuts Ron x Qg

The MDmesh structure achieves a phenomenal reduction of both on-resistance and gate charge, making it the most suitable switch for high efficiency and high frequency converters.

#### MOSFET: conclusions

- A majority-carrier device: fast switching speed

- Typical switching frequencies: tens and hundreds of kHz

- On-resistance increases rapidly with rated blocking voltage

- Easy to drive

- The device of choice for blocking voltages less than 500V

- 1000V devices are available, but are useful only at low power levels (100W)

- Part number is selected on the basis of on-resistance rather than current rating

#### MOSFET: conclusions

- A majority-carrier device: fast switching speed

- to 3MHZ Typical switching frequencies: tens and hundreds of kHz 600 KH2

- On-resistance increases rapidly with rated blocking voltage

- Easy to drive

Vos=600, Row= 141-

(100W)

- The device of choice for blocking voltages less than 500V 1000V devices are available, but are useful only at low power levels 3

- Part number is selected on the basis of on-resistance rather than current rating

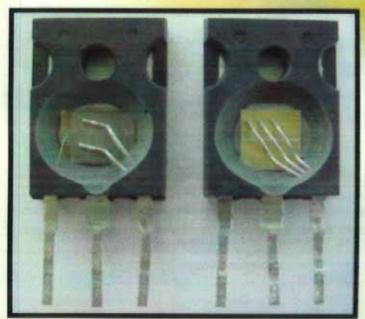

# Inside a failed Power MOSFET

**Fig. 6.** FETs destroyed by the capacitor-dump test. Planar is on the left; Trench is on the right. Note the dual damage sites on the trench part.

| 4.3.4.          | You said fou ??<br>Efficiency vs. switching<br>Would Woff often                            | frequency           |

|-----------------|--------------------------------------------------------------------------------------------|---------------------|

| Add up all of t | the energies lost during the switching                                                     | transitions of one  |

| switching peri  | W. +(W. W. ) (W. +)L-6                                                                     | 2 224               |

|                 | ching power loss is Parasi                                                                 | 600 KHE             |

| AC 1065 Pro = 1 | V <sub>sot</sub> f <sub>sw</sub>                                                           | ften term           |

|                 | ter loss can be expressed as                                                               | 19es 0.055          |

| where           | $P_{cond} + P_{fixed}$ $W_{tot}$ $f_{siv}$ $P_{fixed} = \text{fixed losses (independent)}$ | ent of load and f.) |

| 5 ()            | $P_{cond}$ = conduction losses                                                             | 5hy to TAR          |

|                 |                                                                                            | TESCUC              |

## Fig 4.27 99 79

Fig. 2. DMOSFET structure and its internal resistance distribution.

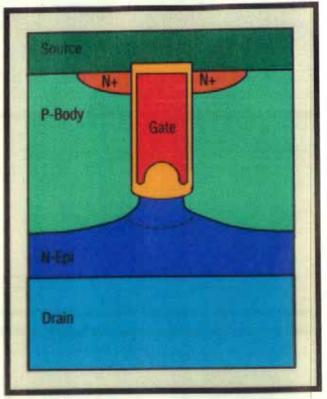

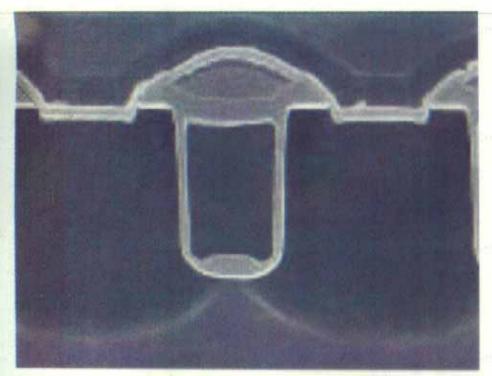

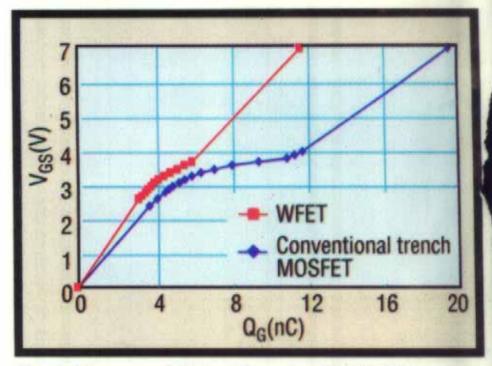

Fig. 4. Schematic cross section of a W-Gated Trench MOSFET (WFET).

## Conventional Trench MOSFET.

Fig. 7. Merit  $R_{DS(on)} \times Q_{ad}$  vs. cell pitch of a WFET.

Fig. 3. Trench of UMOSFET structure and its internal resistance distribution.

Vishay Siliconix' WFET technology uses a thicker gate oxide at the bottom of the silicon trench to reduce device input capacitance. Additional cell density techniques lower R<sub>DS(on)</sub>.

Fig. 1. Planar (left) and Trench (right) test FETs with their die exposed.

Fig. 5. SEM cross section of a W-Gated Trench MOSFET WFET.

|                          | Conventional<br>UMOSFET | WMOSFET | Ratio<br>Conv./WFET |

|--------------------------|-------------------------|---------|---------------------|

| Crss at VDS<br>0V/30V pf | 762/163                 | 207/89  | 3.7/1.8             |

| Qgd nC                   | 4.5                     | 1.6     | 2.85                |

| Rds.Qgd<br>mΩ.nC         | 33.8                    | 12.5    | 2.7                 |

**Table**. Comparison of WFET and conventional trench MOSFET characteristics.

Fig. 6. Measured Gate Charge of a WFET vs. a Conventional Trench MOSFET.

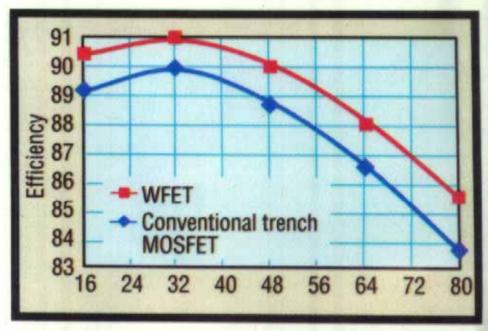

**Fig. 9**. Measured efficiency vs. output current for a PWM switch-mode 4-phase dc-to-dc buck converter with 19V  $V_{IN}$  and 1.3V  $V_{OUT}$ .

Fig. 2. Schematic cross section of conventional Trench MOSFET.

www.newerelectronies.com