| Rating                                  | Specification Value                                                                        |

|-----------------------------------------|--------------------------------------------------------------------------------------------|

| Voltage Rating                          | 15V nominal with ±10% adjustment                                                           |

| Current Rating                          | 20.0 A @ 35°C, derated linearly to 4.0 A @ 75°C                                            |

| Output Voltage: Line Regulation         | 0.1% from minimum to maximum rated line input                                              |

| Output Voltage: Load Regulation         | 0.1% from 0.5 A load to full load.                                                         |

| Output Voltage: Ripple and Noise        | 25 mV <sub>Rus</sub> , 150 mV 20 MHz bandwidth at full load                                |

| Output Voltage: Temperature Coefficient | 0.04%/°C maximum.                                                                          |

| Raied input                             | 87 to 132 V or 175 to 264 V (user selectable range), 40-440 Hz, or 125 to 175 V dc. 400 W, |

| Efficiency                              | 75% minimum at full load.                                                                  |

| Overshoot                               | No overshoot at turn-on turn off of power failure                                          |

| Temperature Range                       | Continuous operation -40°C to +75°C with derating above 35°C. Storage -55°C to +85°C.      |

| Operating Humidity                      | 10% to 85% RH, non-condensing.                                                             |

| In-Hush Limiting                        | The cold-start in-rush current will not exceed 40 A.                                       |

.

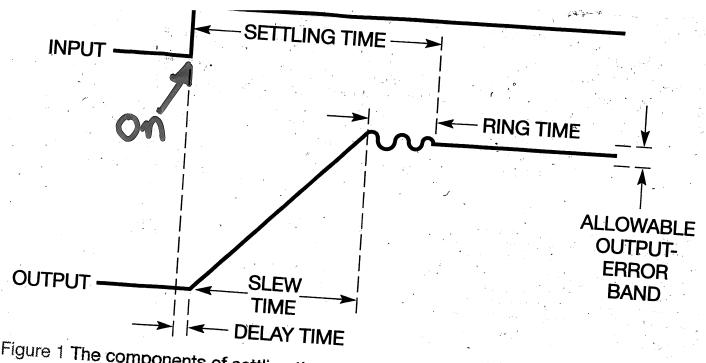

Figure 1 The components of settling time include delay, slew, and ring times. Using fast amplifiers reduces slew time, although longer ring time usually results.

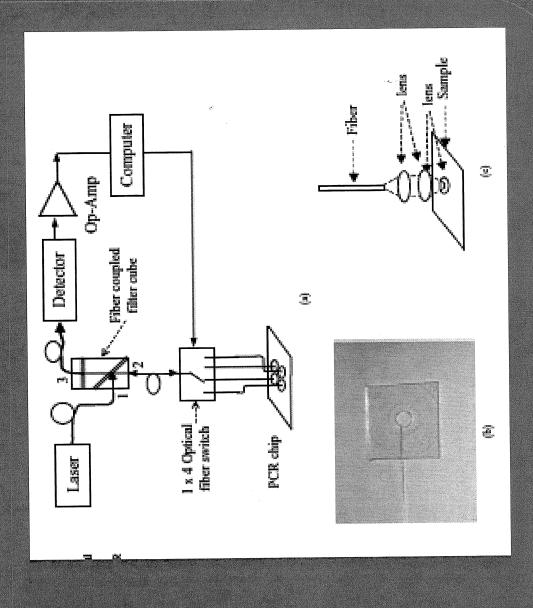

# PCR Fluorescence Detector

Easily integrated into design. Readily available

| Mean Time Between Failures (MTBF)               | 40,000 hours per MIL-HDBK 217F                                                                       |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Hold-Up Time                                    | At full load, output remains within regulation limits for at least 16.7 ms after loss of input nower |

| Tum-On Delay                                    | Output voltage reaches nominal within 0.6 s after application of input power, with no overshoot.     |

| Stability                                       | ±0.1% for 24 hrs after power up.                                                                     |

| Combined Regulation (source, load, temp., time) | ±0.32% for 24 hrs.                                                                                   |

| EMI                                             | Conforms to FCC Class A and MIL-STD-461A.                                                            |

| Fungus Proofing                                 | Passes MIL-STD-810C, Method 508.1.                                                                   |

| Shock                                           | 10 G, 55 Hz, all axes.                                                                               |

| Dimensions                                      | 76 mm × 117.5 mm × 300.0 mm, 3.2 kg.                                                                 |

| Warranty                                        | 5 years                                                                                              |

| Price                                           | \$250 (Quantity 1000)                                                                                |

|                                                 |                                                                                                      |

Alddas typical Specs and

# Electrokinetic Platform

interface to the solid phase (electric double movement of the liquid layer right at the Fluid propulsion (fluid transport) on the electrokinetic platform is based on the layer) initiated by an external voltage As soon as an electric potential is applied along and thus move towards the negative electrode. molecules are attracted by electrostatic forces the channel, the positively charged liquid

Stefan Haeberlea and Roland Zengerle. "Microfluidic platforms for lab-on-a-chip applications," The Royal Society of Chemistry, no. 7, pgs 1094–1110, 2007

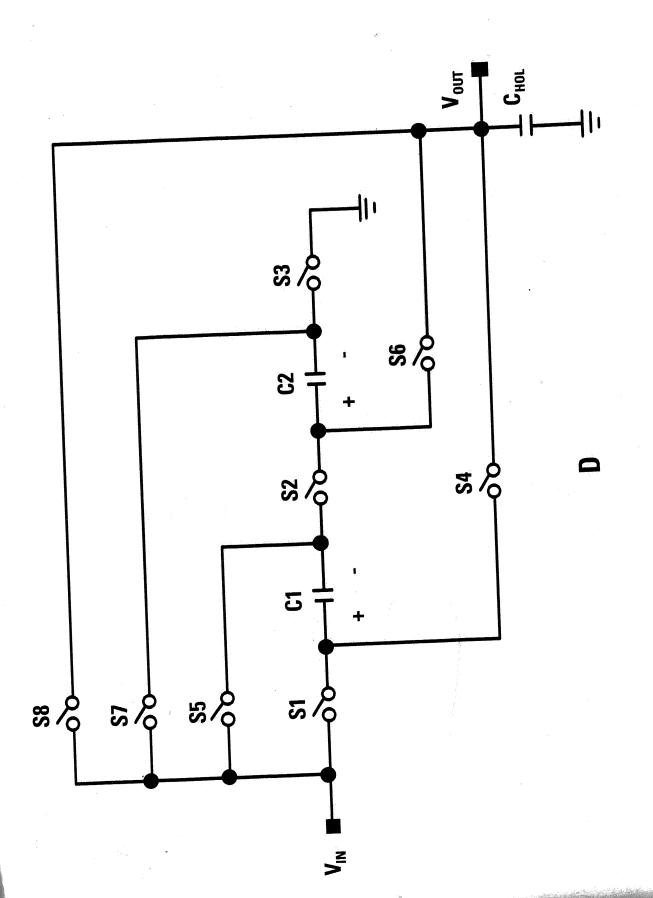

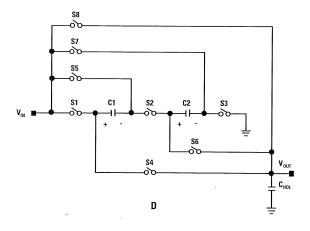

Figure 3. Switched Capacitor Circuit with 1x and 1.5x Gains

# POWER designer

Expert tips, tricks, and techniques for powerful designs

| NO. 115                                 |          |

|-----------------------------------------|----------|

| Feature Artic                           | le1-7    |

| White-LED D I'C Compatible Brightness C | le       |

| White-LED So<br>Capacitor Cu<br>Driver  |          |

| Dual Display<br>White-LED D             | river6   |

| Power Desig                             | n Tools8 |

|                                         |          |

|                                         |          |

# Optimizing Efficiency in White LED Backlight Applications

— By Dario Nurzad, Applications Engineer

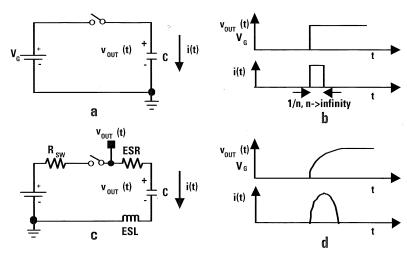

Figure 1. Charging a Capacitor From a Voltage Source (Both the ideal [a, b] and real [c, d] cases are shown)

hite LEDs are typically driven with a constant DC current source to maintain constant luminosity. In portable applications with a single-cell Li-Ion source, the sum of the voltage drop across the white LED and the current source can be lower or higher than the battery voltage. This means that a white LED requires the battery voltage to be occasionally boosted. The best way to accomplish this is to use a step-up DC-DC converter. This method significantly optimizes efficiency at the expense of cost and PCB area. An alternative method of boosting the battery voltage is to use a charge pump, also called a switched capacitor converter. Here we will analyze in more detail the principle of operation of such a device.

### Basic Principles of Charge Pumps

A capacitor is a component that stores electrical charge or energy for release at some predetermined rate and time. If an ideal capacitor is charged with an ideal voltage source  $V_G$  (Figure 1a) the charge storage occurs instantly

### **NEXT ISSUE:**

**Switching Controller Layouts**

## POWER | designer

### Optimizing Efficiency in White LED Backlight Applications

corresponding to a Dirac impulse function for the current (*Figure 1b*). The total stored charge is given by:  $Q = CV_G$ .

Real capacitors have Equivalent Series Resistance ESR) and Equivalent Series Inductance (ESL). Neither affects the ability of the capacitor to store energy; however, they have a large effect on the overall efficiency of the switched capacitor voltage converter. An equivalent circuit for the charge of an actual capacitor is shown in *Figure 1c*, where *R<sub>SW</sub>* is the resistance of the switch. The charging current path will have a series inductance, which can be reduced with proper component layout.

As soon as the circuit is energized, transient conditions of an exponential nature occur until a steady-state condition is reached. The capacitor parasitics limit the peak charge current and increase the charge transfer time (Figure 1d). Therefore, the capacitor charge build-up cannot occur instantly, meaning that the initial voltage variation across the capacitor is equal to zero. Charge pumps use this property of capacitors as shown in Figure 2a.

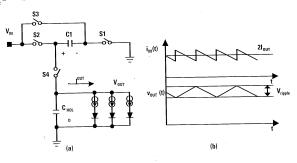

Figure 2. Charge Pump Circuit (a) with Relevant Waveforms (b)

The voltage conversion is achieved in two phases. During the first phase, switches  $S_1$  and  $S_2$  are closed, whereas switches  $S_3$  and  $S_4$  are open and are charged to the input voltage:

$$V_{C1+} - V_{C1-} = V_{C1+} = V_{IN}$$

During the second phase, switches  $S_3$  and  $S_4$  are closed, whereas switches  $S_1$  and  $S_2$  are open. Because the voltage drop across the capacitor cannot change instantly, the output voltage jumps to twice the value of the input voltage:

$$V_{C1+} - V_{C1-} = V_{OUT} - V_{IN} = V_{IN} \rightarrow V_{OUT} = 2V_{IN}$$

Voltage doubling can be accomplished using this technique. The duty cycle of the switching signal is usually 50%; which generally yields the optimal charge transfer efficiency. Let us examine in more detail the charge transfer procedure and how the switched capacitor converter parasitics influence its operation.

The steady-state current and voltage waveforms for a switched capacitor voltage doubler are shown in *Figure 2b*. Due to power conservation, the average input current is twice the output current. During the first phase, a charging current flows into  $C_1$ . The initial value of this charging current depends upon the initial voltage across  $C_1$ , the ESR of  $C_1$ , and the resistance of the switches. The charging current then decays exponentially as  $C_1$  is charged. The charging time constant is several times greater than the switching period. Smaller time constants will cause the peak currents to increase. During this time the output capacitor  $C_{HOLD}$  supplies the load current discharging linearly by an amount equal to:

$$\Delta V_{OUT} = \frac{I_{OUT}}{2 f C_{HOLD}}$$

During the second phase when  $C_{1+}$  is connected to the output, a discharge current (whose magnitude is the same as the previous charging current,) flows through  $C_{1}$  to the load. In this phase, the step change in the output capacitor current is approximately  $2I_{OUT}$ . Although this current step should create an output voltage step equal to  $2I_{OUT}ESR_{C\_HOLD}$ , the use of low-ESR ceramic capacitors renders this step change negligible. At this point,  $C_{HOLD}$  charges

# POWER designer

### **Optimizing Efficiency in White LED Backlight Applications**

linearly by an amount equal to:  $\Delta V_{OUT} = \frac{I_{OUT}}{2fC_{HOLD}}$

When  $C_1$  is connected back between the input and ground,  $C_{HOLD}$  discharges linearly by an amount equal to:  $\Delta V_{OUT} = \frac{I_{OUT}}{2 \, f C_{HOLD}}$

The total peak-to-peak output ripple voltage is given by:

$V_{RIPPLE} \cong \frac{I_{OUT}}{2fC_{HOLD}}$

Higher switching frequencies allow smaller output capacitors for the same amount of ripple.

Parasitics of the charge pump cause the output voltage to fall as the load current increases. As a matter of fact, there is always an RMS current of  $2I_{OUT}$  flowing through  $\mathcal{C}_1$  and two switches  $(2R_{SW})$  resulting in a power dissipation of:

$$P_{SW} = (2I_{OUT})^2 (2R_{SW} + ESR_{C1}) = I^2_{OUT} (8R_{SW} + 4ESR_{C1})$$

In addition to these purely resistive losses, an RMS current of  $I_{OUT}$  flows through the equivalent resistance of the switching capacitor  $C_1$ :

$$P_{C1} = I^{2}_{OUT} R_{C1} = I^{2}_{OUT} \frac{1}{fC_{1}}$$

th

The RMS current flowing through  $C_{HOLD}$  is equal to  $I_{OUT}$ , resulting in a power dissipation of:

$$P_{ESR\_HOLD} = I^{2}_{OUT}ESR_{C\_HOLD}$$

All of the losses can be grouped in an equivalent output resistance:

$$R_{OUT} = 8R_{SW} + 4ESR_{C1} + \frac{1}{fC_1} + ESR_{C_-HOLD}$$

Thus the output voltage of the charge pump can be modeled as follows:  $V_{OUT} = 2V_{IN} - I_{OUT}R_{OUT}$

In general, because of the low ESR of ceramic capacitors and the high switching frequency, the output ripple and output voltage drop depends on the switch resistances. Utilizing more switches and capacitors enables additional voltage conversions.

Figure 3. Switched Capacitor Circuit with 1x and 1.5x Gains

Figure 3 demonstrates this property using capacitors.

Once more, the voltage conversion is achieved in two phases. During the first phase switches S1 to S3 are closed, whereas switches S4 to S8 are open. Therefore  $\mathcal{C}_1$  and  $\mathcal{C}_2$  are stacked and—assuming  $\mathcal{C}_1$  equal to  $\mathcal{C}_2$ —charged to half the input voltage:

$$V_{C1+} - V_{C1-} = V_{C2+} - V_{C2-} = \frac{V_{IN}}{2}$$

The output load current is provided by the output capacitor  $\mathcal{C}_{HOLD}$ . As this capacitor discharges and the output voltage falls below the desired output voltage, the second phase is activated to boost the output voltage above this value. During the second phase,  $\mathcal{C}_1$  and  $\mathcal{C}_2$  are in parallel, tied between  $V_{IN}$  and  $V_{OUT}$ . Switches S4 to S7 are closed, whereas switches S1 to S3 and S8 are open. Because the voltage drop across the capacitor can not change instantly, the output voltage jumps to 1.5X the value of the input voltage:

$$V_{C1+} - V_{C1-} = V_{C2+} - V_{C2-} = V_{OUT} - V_{IN} = \frac{V_{IN}}{2} \Longrightarrow V_{OUT} = \frac{3}{2} V_{IN}$$

The voltage boost operation is accomplished this way: A voltage conversion with a gain of 1x is achieved by closing switch S8 and leaving switches S1 to S7 open.

# POWER | designer

### Optimizing Efficiency in White LED Backlight Applications

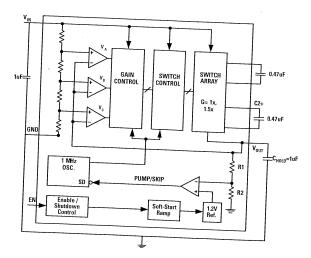

Figure 4. Switched Capacitor Regulator Block Diagram

### Pulse Frequency Modulation (PFM) Scheme

A simplified Pulse Frequency Modulated (PFM) regulation scheme, which utilizes multiple gains, is depicted in *Figure 4*. The down-scaled output voltage is compared by the PUMP/SKIP comparator to a 1.2V voltage reference. The PUMP/SKIP comparator is ramped up linearly on start up to provide the soft-start function. When the output voltage is above the desired limit the device does not switch, consuming minimal supply current. During this idle state the output load current is provided by the output capacitor. As this capacitor discharges and the output voltage falls below the desired output voltage, the charge pump is activated until the output voltage is above this value again.

The primary advantage of the PFM regulation architecture is evident at light loads. Typically the load is provided with energy by the output capacitor. The supply current is very low, as the output capacitor only needs to be re-charged occasionally by enabling the charge pump.

In general, regulated charge pumps do not maintain a high efficiency over a wide input range. Because the input-to-output current ratio is scaled

according to the basic voltage conversion, any output voltage magnitude less than the input-voltage-times-the-charge-pump-gain will result in additional power dissipation within the converter and efficiency will be degraded proportionally:

$$\eta_{IDEAL} = \frac{V_{OUT} I_{OUT}}{V_{IN} I_{IN}} = \frac{V_{OUT} I_{OUT}}{V_{IN} G I_{OUT}} = \frac{V_{OUT}}{V_{IN} G}$$

$$\eta_{IDEAL} \rightarrow 1 \Leftrightarrow V_{OUT} = G V_{IN}$$

The ability of the converter to change gains according to the input/output ratio allows for optimal efficiency over the entire input voltage range. Ideally, the gain should vary linearly. In reality, given a certain number of capacitors and switches, only a finite number of gain configurations are possible.

Referring to *Figure 4* the input voltage is scaled and fed into the non-inverting nodes of three comparators. All inverting nodes of the comparators are connected to the output voltage. Based on the input-to-output voltage ratio the outputs of the comparators provide the gain control circuitry with a three-bit word, which is used to select the minimum gain G, able to achieve the desired voltage conversion. In white LED applications, however, the selection of the proper gain G is not only based on the input and output voltages.

### Conclusion

There are certain advantages in using switched capacitor rather than inductor-based switching techniques. An obvious advantage of switched capacitor converters is the elimination of the inductor and the related magnetic design issues. They usually have relatively low noise and minimal radiated EMI. Additionally, the applications circuits are simple and only a few small capacitors are needed.

Because there is no inductor, the final PCB component height is generally smaller than a comparable switching converter.