## ECE 331: Electronics Principles I Fall 2014

## Lab #3: MOSFETs Characterization

## Pre-lab due on Thursday, Oct. 16, before noon

## Pre-lab

- A. Draw both the large and small signal models for NMOS transistors. Sketch  $I_D$  vs  $V_{DS}$  characteristics for several values of  $V_{GS}$  and graphically illustrate the Channel Length Modulation effect.

- B. List the difference between NMOS and PMOS transistors. Draw a schematic of each one, Labeling all relevant voltages and currents. What is an advantage of using a PMOS? What is a drawback? (Hint: Consider the response time)

- C. For an NMOS transistor with threshold voltage Vt = 0.62 V, Kn' = 0.167mA/V<sup>2</sup>, here Kn' is defined to be equal to  $\mu_n C_{ox}$ , If Vover-drive is 0.25 V, W = 0.55  $\mu$ m and L = 0.18  $\mu$ m, answering the questions listed below:

- 1. What is the actual channel length for Vds equal to 0.5 V, 1V and 1.5V separately? Assume  $\lambda = 0.1 \text{ V}^{-1}$  for this process. What is the output impedance  $r_o$  at Vds = 1 V?

- 2. Assume  $\lambda = 0$ , find  $g_m$  at  $I_D = 1$  mA.

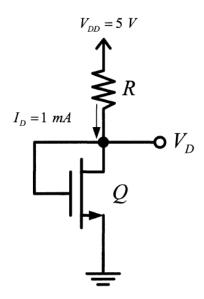

- D. For the circuit below, given Vt = 1 V, Kn'(W/L) = 2 mA/V<sup>2</sup> and  $\lambda = 0$ , Find R to make  $I_D = 1$  mA and how much  $V_D$  is.

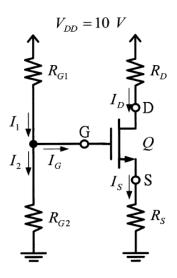

E. For the circuit below, given Vt = 1 V, Kn'(W/L) = 0.5 mA/V² and  $\lambda$  = 0,  $R_{G1}$  = 5 M $\Omega$ ,  $R_{G2}$  = 5 M $\Omega$ ,  $R_{D}$  = 6 K $\Omega$  AND  $R_{S}$  = 6 K $\Omega$ , Find voltages at the each terminal (V $_{G}$ , V $_{S}$ , V $_{D}$ ) and current at each node (I $_{G}$ , I $_{S}$ , I $_{1}$ , I $_{2}$ ).

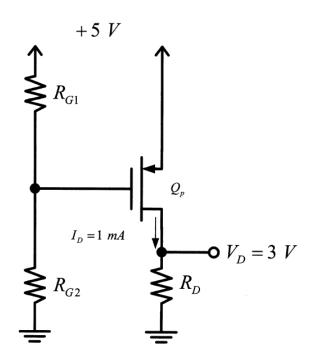

F. Design the circuit below to make Qp working in saturation region and  $I_D=1$  mA,  $V_D=3$  V, given Vt=-1 V, Kp'(W/L)=2 mA/V $^2$  and  $\lambda=0$ , Find  $R_{D_s}R_{G1_s}R_{G2}$