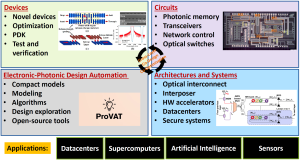

My primary research goals are focused on the development of high-performance computing systems and interconnection networks employing emerging technologies while emphasizing on energy-efficiency and robustness. Some topics of interest are:

- Silicon Photonics

- High-Performance Computing

- Optical Switching

- AI Hardware Accelerators

- Interconnection Networks

- System Modeling and Simulation

- Design for Reliability and Energy Efficiency

This page reviews some of my research activities. Relevant journal and conference publications can be found here.