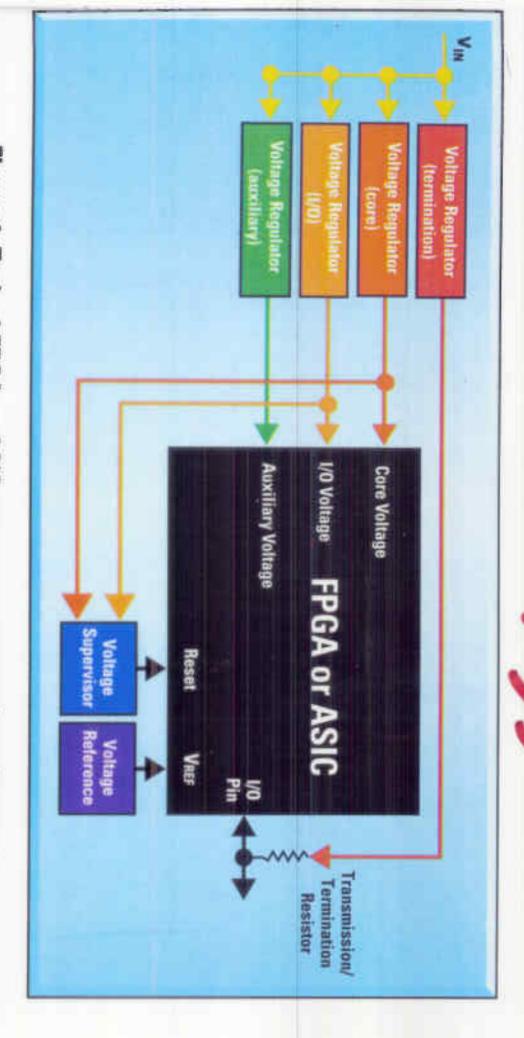

Figure 1: Typical FPGA or ASIC power management requirements

# Power Management Considerations for FPGAs and ASIC

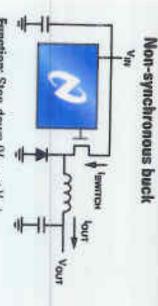

Function: Step-down ( $V_{DUT} < V_{INI}$ )

When to use: Typically when  $V_{DII}$  is 3x to 5x  $V_{DUT}$  and  $I_{DUT}$  is > 0.5A and < 5A

Characteristics: Easy to design and good efficiency for the above-mentioned typical V<sub>m</sub>/V<sub>gUT</sub>/I<sub>DUT</sub> conditions

Devices to use: All buck integrated regulators and controllers

Function: Step-down (V<sub>DUT</sub> < V<sub>HI</sub>)

When to use: When high efficiency is required with high-output current (> 5A) or low duty cycles (V<sub>th</sub> > 5 × V<sub>DUT</sub> and/or l<sub>DUT</sub> < 0.5A)

Characteristics: A second switch replaces the diode in the basic buck topology, reducing losses in the conditions mentioned above

Devines to use: Any "synchronous rectification" buck integrated regulator or controller

Figure 2: Step-down configurations

Feection: Step-down (V<sub>OUT</sub> < V<sub>IN</sub>)

When to use: Typically when I gut < 1A, ultra low-dropout, and low-noise applications

Characteristics: Excellent option where fixed output, low current, and low voltage drops are required. Easy to implement

Devices to use: Any low-dropout, linear regulator Comments: Great for micropower applications

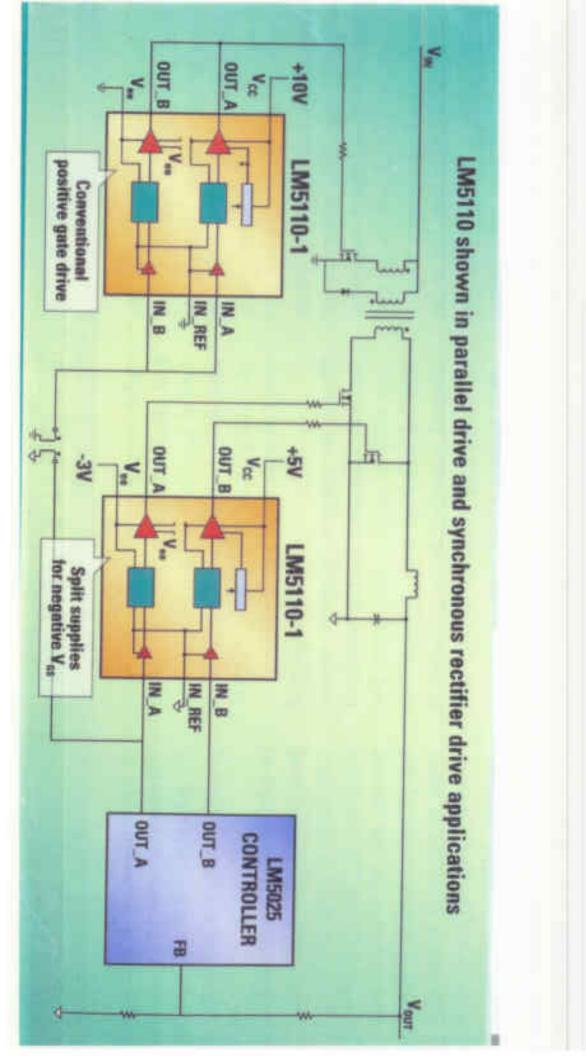

- Each channel can sink/source 5A /3A for very fast rise/fall times (20 ns/10 ns into a 2 nF load)

- Short propagation delay times (25 ns typical)

- Integrated under voltage lockout protection (2.8V typical)

- Shutdown pin disables drivers for low-power standby mod

- Offered in three industry standard configurations: dual non-inverting, dual inverting, and one inverting & one non-inverting

# Power Management Considerations for FPGAs and ASICs

the two phases can be made to operate out-ofphase, the RMS ripple current in the innut canacitor

simply or flexibly implemented if the regulators

V-500

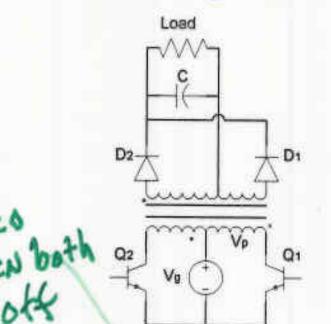

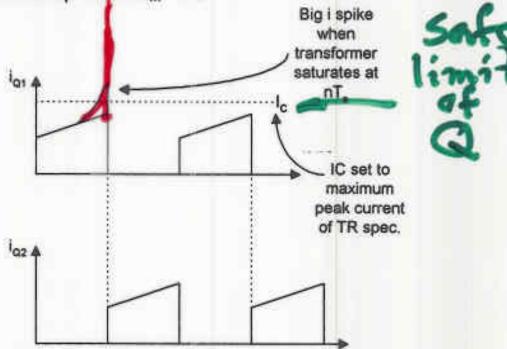

To monitor

SATURATION of

Transformer Core

we will employ current

sensors in Q<sub>1</sub> and Q<sub>2</sub>

collector's to look for

high current spikes.

We compare to I<sub>control</sub>(ref) and we shut off Q<sub>1</sub> and/or Q<sub>2</sub> if I > I<sub>control</sub>.

$i_{Lm} = \frac{\int V_{Lm} dt}{Lm} \neq 0$  over Ts

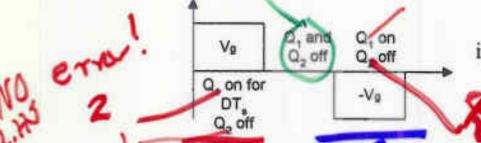

Due  $V_{on}(Q_1) \neq V_{on}(Q_2)$  and  $\Delta t (Q_1) \neq \Delta t(Q_2)$  we might have a slight offset each clock cycle and  $i_{Lm}$  is not zero.

= VON (Q2)?

### a death by i spike

Even a small imbalance adds up after 100 switch periods and the transformer will ultimately saturate. Then for example the current on  $i(Q_1)$  will shoot up when  $L_m \rightarrow 0$

Use I<sub>c</sub>(control) as a maximum to sense if i<sub>Q1</sub> gets excessive and shut it down if it does. In practice we never build push pull converter with duty cycle control and voltage. Rather we use current programmed control of Chapter 11. Below we compare switch stress in the topologies of lectures 15 and 16.

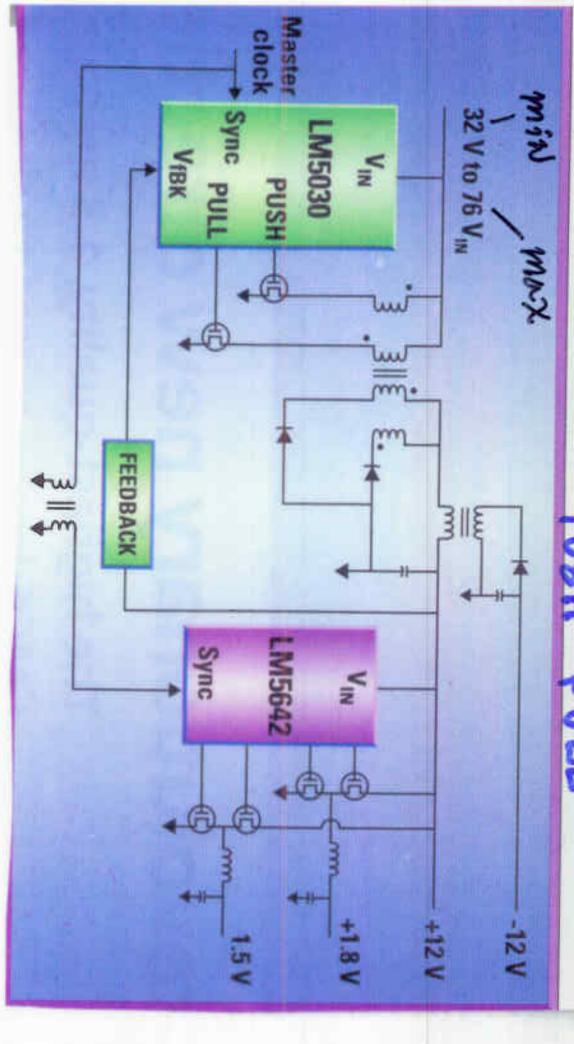

### DSL Line Card: -48 V mu put isolated pow

rsupply

### Primary controller: LM5030 100 V current-mode Secondary controller: LM5642 dual synchronous bu

- 48 V<sub>IN</sub>, multiple outputs ±12 V, 1.8 V, and 1.5 V<sub>OUT</sub>

- High efficiency >90%

- Tight regulation <2%</li>

- Oscillators synchronized to a master clock

- User-programmable softstart and power on/off sequence

- Available separately or together:

- LM5030 (MSOP-10)

- LM5642 (TSSOP-28)

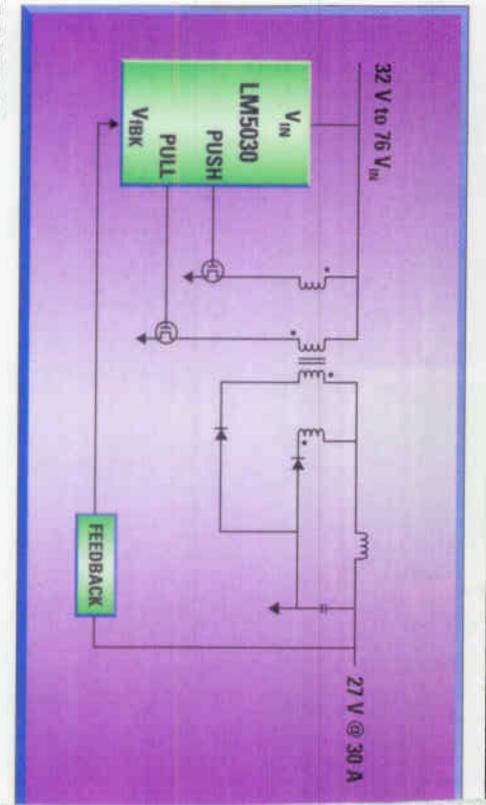

## 3G Basestations: 850 W Push-Pull DC/DC co

### LM5030

- Fully integrated LM5030 includes: high bandwidth error amp, precision reference, programmable softstart, and dual-mode current sense

- Internal high-voltage (100 V) start-up regulator

Secondary controller: Primary controller: LM5030 100 V current-mode Push-Pull

$\bullet$  48 V<sub>IN,</sub> multiple outputs  $\pm 12$  V, 1.8 V, and 1.5 V<sub>OUT</sub> High efficiency >90% LM5642 dual synchronous buck

Tight regulation <2%</li>

Oscillators synchronized to a master clock

User-programmable softstart and power on/off sequencing

• Available separately or together:

LM5030 (MSOP-10)

LM5642 (TSSOP-28)

First we review the switch stress of the push-pull compared to the half and full bridge covered earlier.

|             | Switch           |                                           | MOSFET             |                                          | Rectifier(s)   |                    |

|-------------|------------------|-------------------------------------------|--------------------|------------------------------------------|----------------|--------------------|

| Topology    | Vito             | (                                         | Voss               | 16                                       | V <sub>R</sub> | 4                  |

| Push-pull   | 2V <sub>in</sub> | 1.2Pout<br>Vin(min)                       | (2V <sub>b</sub> ) | $\frac{1.2P_{\rm out}}{V_{\rm in(min)}}$ | $2V_{\rm out}$ | I <sub>out</sub>   |

| Half-bridge | V <sub>in</sub>  | 2P <sub>out</sub><br>V <sub>in(min)</sub> | $V_{\rm in}$       | $\frac{2P_{\rm out}}{V_{\rm in(min)}}$   | 2Vous          | $I_{\mathrm{out}}$ |

| Full-bridge | V <sub>ia</sub>  | 1.2Post                                   | Mr. Lon            | 1.2Pout                                  | $2V_{\rm out}$ | $I_{\mathrm{out}}$ |

Note that the push-pull is equivalent to the full bridge in switch stress and better than the half bridge. However, the push-pull is a dangerous circuit as it has a tendency towards core saturation which will cause the transformer input to look like a short and will likely kill the switches. This arises when the flux within the core is inadvertently non-symmetric so that a small DC offset occurs. Unfortunately, this small offset will cause a walk towards saturation over many switch cycles. Usually, current mode feedback must be employed rather than voltage feedback to control this difficulty of push-pull. Also possible, is active core rebalancing as illustrated on the next page.

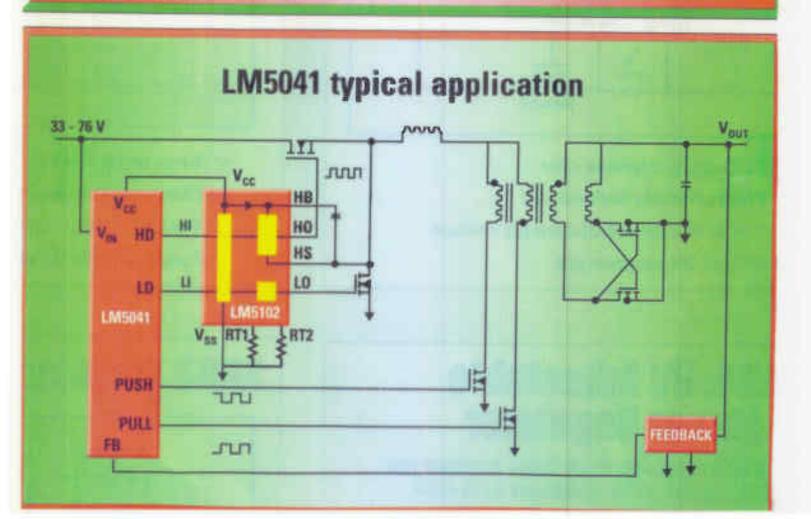

### New cascaded controller/100 V driver "chipset" family

| Configuration           | Voltage-fed<br>or current-fed | Controller | Driver(s)              | Benefits/<br>applications                   |  |  |

|-------------------------|-------------------------------|------------|------------------------|---------------------------------------------|--|--|

| Cascaded push-pull      | Voltage-fed                   | LM5041     | LM5102                 | High efficiency/<br>medium power            |  |  |

| Cascaded &              | Current-fed                   | LM5041     | LM5102                 | High efficiency/<br>medium power            |  |  |

| Cascaded<br>half-bridge | Voltage-fed                   | LM5041     | LM5102 &<br>LM5100     | High efficiency/<br>medium to<br>high power |  |  |

| Cascaded<br>full-bridge | Current-fed                   | LM5041     | LM5102 &<br>(2) LM5100 | High efficiency/<br>high power              |  |  |

Flexibility for multiple configurations: interleaved forward, cascaded push-pull, half-bridge, and full-bridge

Estimating the Significant Minimum Parameters of the Power

|                | Semiconductors            |                         |                                              |                         | _                                                         |                   |                    |

|----------------|---------------------------|-------------------------|----------------------------------------------|-------------------------|-----------------------------------------------------------|-------------------|--------------------|

|                |                           | Bipolar Power<br>Switch |                                              | MOSFET Power<br>Switch  |                                                           | Rectifier(s)      |                    |

|                | Topology                  | Vaso                    | le                                           | Voss                    | lo                                                        | Va                | 14                 |

| 1200           | Flyback                   | 1.7V <sub>in(mex)</sub> | $\frac{2P_{\text{out}}}{V_{\text{in(min)}}}$ | 1.5V <sub>in(max)</sub> | 2Pout<br>Vin(min)                                         | $10V_{\rm sut}$   | I <sub>out</sub>   |

| Miss           | One Transistor<br>Forward | 2Vin                    | $\frac{1.5P_{out}}{V_{\rm in(min)}}$         | 2V <sub>in</sub>        | $\frac{1.5P_{\rm out}}{V_{\rm in(min)}}$                  | 3V <sub>out</sub> | Lout               |

| necds<br>new H | Push-pull                 | (2V <sub>in</sub> )     | $\frac{1.2P_{\rm out}}{V_{\rm in(min)}}$     | $2V_{\rm in}$           | $\frac{1.2P_{\rm out}}{V_{\rm in(min)}}$                  | $2V_{aut}$        | I <sub>out</sub> - |

| PETS           | Half-bridge               | Vin                     | $\frac{2P_{\rm out}}{V_{\rm in(min)}}$       | V <sub>ia</sub>         | $\frac{2P_{\mathrm{out}}}{V_{\mathrm{in}(\mathrm{min})}}$ | 2V <sub>out</sub> | I <sub>out</sub>   |

|                | Full-bridge               | v/                      | $\frac{1.2P_{\rm out}}{V_{\rm in(min)}}$     | V <sub>in</sub>         | $\frac{1.2P_{\rm out}}{V_{\rm in(min)}}$                  | 2V <sub>044</sub> | Lout               |

Whoa.

Bridge

Sucks i

necds

new FETS

ly back rectife 15 hard 40 diodes

Topy mosfet on Ic

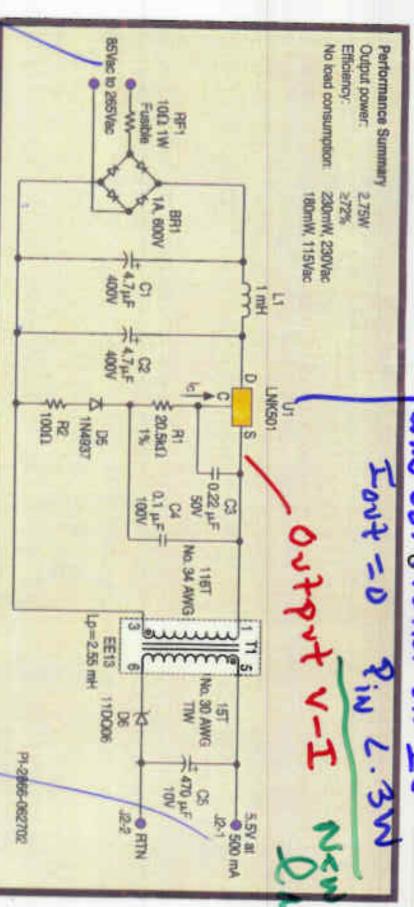

Fig. 1. Schematic of 2.75W LinkSwitch LNK501 charger.

Battery

In put

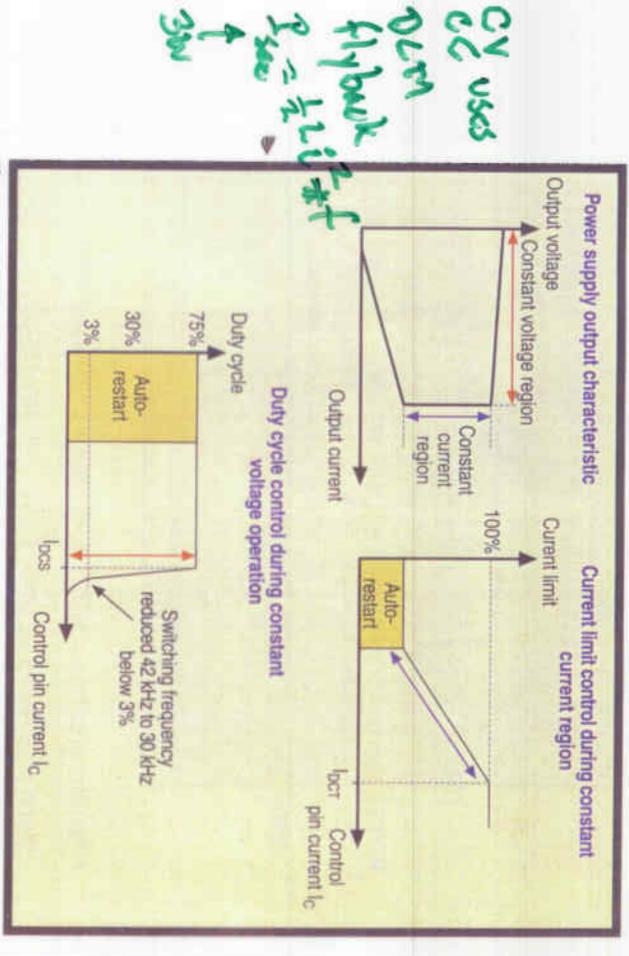

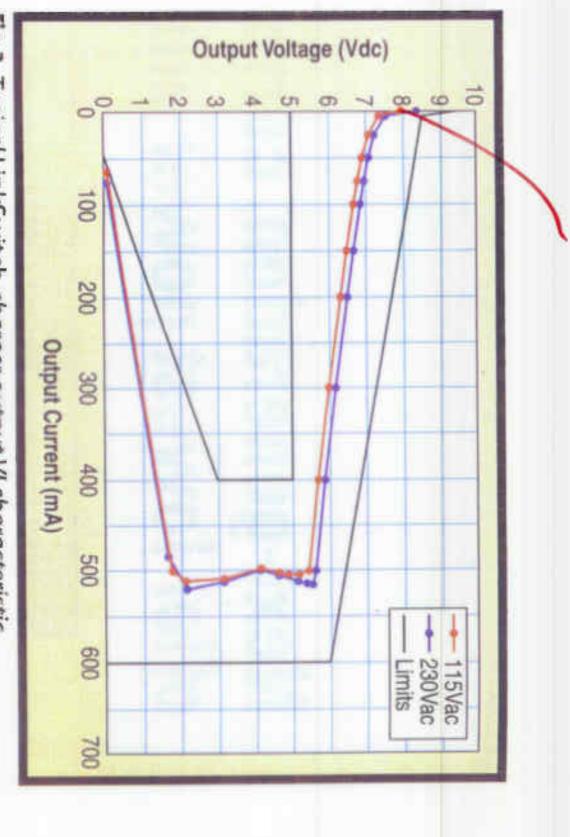

and current limit control to generate a CV/CC output. Fig. 3. LinkSwitch Control pin characteristic provides both duty cycle

IL-0 VIN = 230 AC

V, w = 115 ac

PW L 250mw

200 m W

Fig. 2. Typical LinkSwitch charger output VI characteristic.