# 6.4. Converter evaluation and design

For a given application, which converter topology is best?

applications There is no ultimate converter, perfectly suited for all possible

Trade studies

- Rough designs of several converter topologies to meet the given specifications

- An unbiased quantitative comparison of worst-case transistor currents and voltages, transformer size, etc.

cost Comparison via switch stress, switch utilization, and semiconductor

Spreadsheet design

# 6.4.2. Converter design using computer spreadsheet

Given ranges of  $V_{\rm g}$  and  $P_{load}$ , as well as desired value of V and other quantities such as switching frequency, ripple, etc., there are two basic engineering design tasks:

- Compare converter topologies and select the best for the given specifications

- Optimize the design of a given converter

entered, and detailed design investigations can be quickly performed: of the steady-state converter analyses of Chapters 1-6 can be A computer spreadsheet is a very useful tool for this job. The results

- Evaluation of worst-case stresses over a range of operating points

- Evaluation of design tradeoffs

### Spreadsheet design example

#### Choices

| Canthan                     |

|-----------------------------|

| Specifications              |

| Maximum input voltage $V_p$ |

| Minimum input voltage $V_e$ |

| Output voltage V            |

| Maximum load power Pload    |

| Minimum load power Pland    |

| Switching frequency f,      |

| Maximum output ripple Δν    |

|      | •              |

|------|----------------|

| ±20% | input voltage: |

|      | rectified 23   |

|      | 0 Vrms         |

Regulated output of 15 V

390 V 260 V

Rated load power 200 W

200 W

15 V

20 W

- Must operate at 10% load

- Select switching frequency of 100 kHz

0.1 V

100 kHz

Output voltage ripple ≤ 0.1V

Specifications are entered at top of spreadsheet Compare single-transistor forward and flyback converters in this application

### Forward converter design, CCM

#### Design variables

Reset winding turns ratio  $n_2/n_1$ Turns ratio  $n_3/n_1$ Inductor current ripple  $\Delta i$

Design for CCM at full load; may operate in DCM at light load

### Enter results of converter analysis into spreadsheet (Forward converter example)

Maximum duty cycle occurs at minimum  $V_g$  and maximum  $P_{load}$ Converter then operates in CCM, with

$$D = \frac{n_1}{n_3} \frac{V}{V_g}$$

Inductor current ripple is

$$\Delta i = \frac{DVT_s}{2L}$$

Solve for L:

Conscionace #)

$$L = \frac{D'VT_s}{2\Delta i}$$

$\Delta i$  is a design variable. For a given  $\Delta i$ , the equation above can be used less than the full-load output current. C can be found in a similar to determine L. To ensure CCM operation at full load, ∆i should be

## Forward converter example, continued

operating in DCM is Check for DCM at light load. The solution of the buck converter

$$V = \frac{n_3}{n_1} V_8 \frac{2}{\sqrt{1 + \frac{4K}{D^2}}}$$

with  $K = 2L/RT_{in}$  and  $R = V^2/P_{load}$

that all quantities are referred to the transformer secondary side These equations apply equally well to the forward converter, provided

Solve for D:

$$D = \frac{2\sqrt{K}}{\sqrt{\left(\frac{2n_3V_g}{n_1V} - 1\right)^2 - 1}} \text{ in DCM} \qquad D = \frac{n_1}{n_3} \frac{V}{V_g} \text{ in CCM}$$

at a given operating point, the actual duty cycle is the small of the occurs at minimum  $P_{load}$  and maximum  $V_g$ . values calculated by the CCM and DCM equations above. Minimum D

# More regarding forward converter example

Worst-case component stresses can now be evaluated.

Peak transistor voltage is

$$\max\left(\nu_{Q1}\right) = V_g\left(1 + \frac{n_1}{n_2}\right)$$

RMS transistor current is

$$I_{Q1,rms} = \frac{n_3}{n_1} \sqrt{D} \sqrt{I^2 + \frac{(\Delta i)^2}{3}} \approx \frac{n_3}{n_1} \sqrt{D} I$$

(this neglects transformer magnetizing current)

Magnetics design is left for a later chapter. Other component stresses can be found in a similar manner.

How to turce Vorim = 0? ansformer reset mechanism Equal/Opposito 1000 H boost inductor

- DT\_ --DT

As in full-bridge buck topology, transformer volt-second balance is obtained over two switching periods.

During first switching period: transistors  $Q_t$  and  $Q_t$  conduct for time  $DT_s$ , applying volt-seconds VDT to secondary winding.

During next switching period: transistors  $Q_2$  and  $Q_3$  conduct for time  $DT_s$ , applying volt-seconds  $-VDT_s$  to secondary winding.

Fundamentals of Power Electronics

Pro-active Core Reset Methodology Chapter 6: Converter circuits

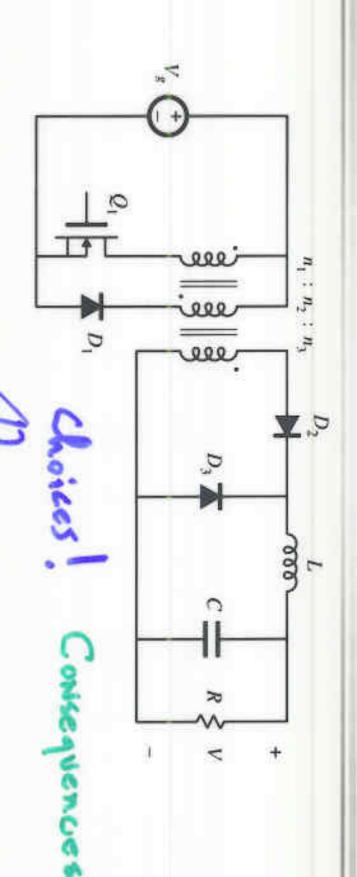

#### TYPE OF CONVERTER

Circuit Configuration

#### IDEAL TRANSFER UNCTION

$\frac{V_{0}}{V_{1N}} = 2\frac{N^{2}}{N_{1}}(\frac{V_{0}}{V_{S}}) = 2\frac{N^{2}}{N_{1}}(D)$

$$I_{DMAX} = \frac{N_2}{2} \left( I_{RL} + \frac{\Delta I_{LJ}}{2} \right) + I_{MA}$$

$$I_{MAG} = \rho_{est} \text{ magnetizing current.}$$

VDS = VIN

#### DISADVANTAGES

APPLICATIONS

High power, high input voltage

APPLICABLE

HARRIS PRODUCTS

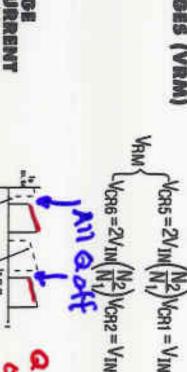

#### VOLTAGES (VRM)

Full Bridge

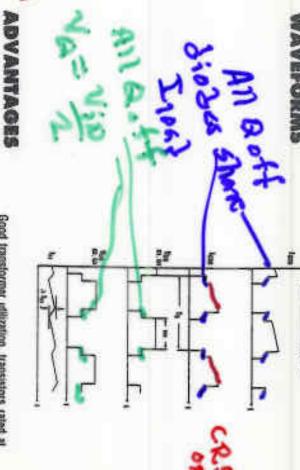

V<sub>III</sub>, isolation, multiple outputs. ID is reduced as a ratio of N<sub>2</sub>/N<sub>1</sub>. Zero voltage switching possible Low Good transformer utilization, transistors rated at cutput ripple

High parts count. C1 has high ripple current. Re-quires high side switch drive. Cross conduction of Q1 and Q2 or Q3 and Q4 possible. High triput cur-

HIP4080/81 HIP2500 HV400

### Summary of key points

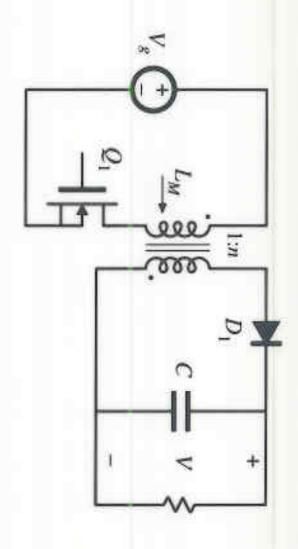

- The steady-state behavior of transformer-isolated converters analysis of the discontinuous conduction mode use of equivalent circuits to model losses and efficiency, and then be applied, including use of inductor volt-second balance and capacitor charge balance to find dc currents and voltages, circuit. The techniques developed in the previous chapters can may be understood by first replacing the transformer with the magnetizing-inductance-plus-ideal-transformer equivalent 1 Dock L

- In the full-bridge, half-bridge, and push-pull isolated versions of it transfers energy: the applied voltage polarity alternates on successive switching periods. the buck and/or boost converters, the transformer frequency is twice the output ripple frequency. The transformer is reset while

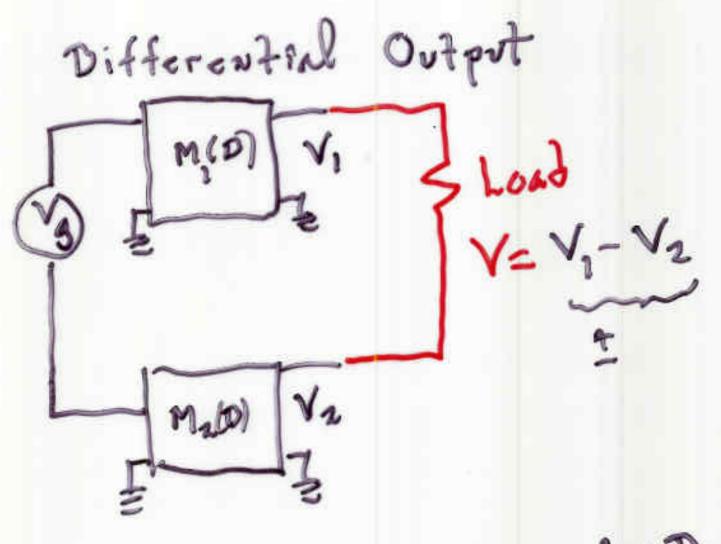

Case M, (D) buck driven by D,

M2(D) buck driven by D,

M2(D) buck driven by D,

Vout = DV, - DV, = (2D-1)V,

### Flyback converter design, CCM

#### Design variables

Turns ratio  $n_2/n_1$ Inductor current ripple  $\Delta i$

0.125

ipple  $\Delta i = 3$  A ref to sec

Design for CCM at full load; may operate in DCM at light load