## **ECE 451 Verilog Tutorial**

James Barnes (jobarnes@engr.colostate.edu)

### Outline

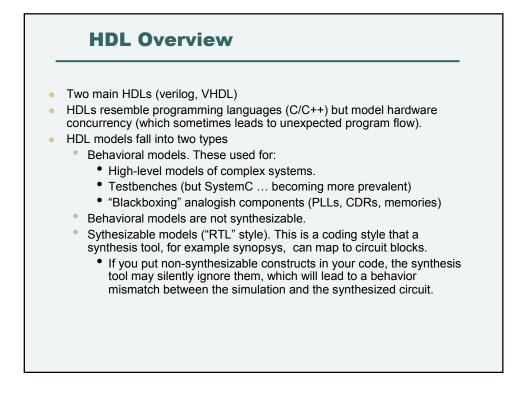

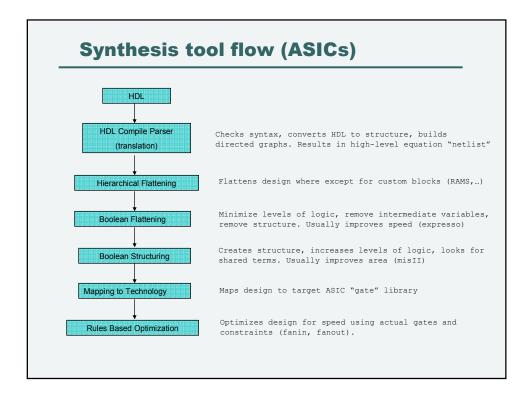

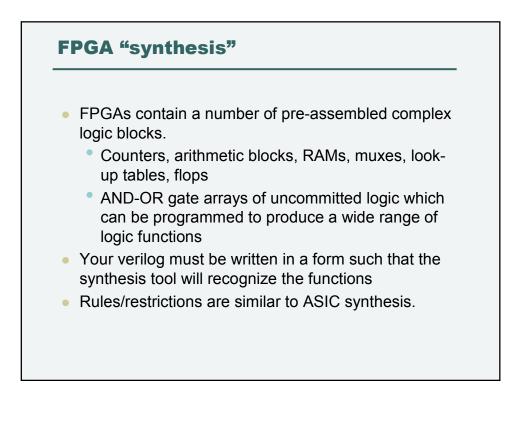

- HDL overview, design flow

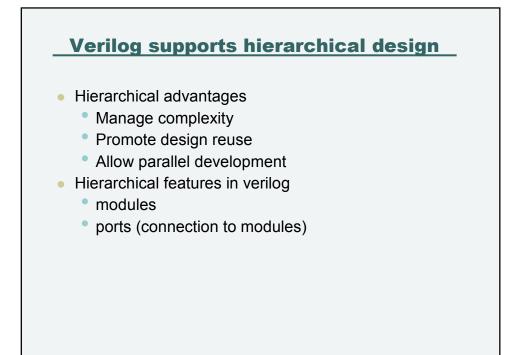

- Hierarchical design and design for verification

- Numbers, data types and operators

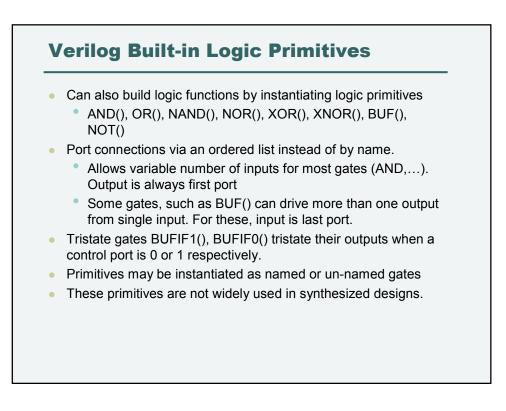

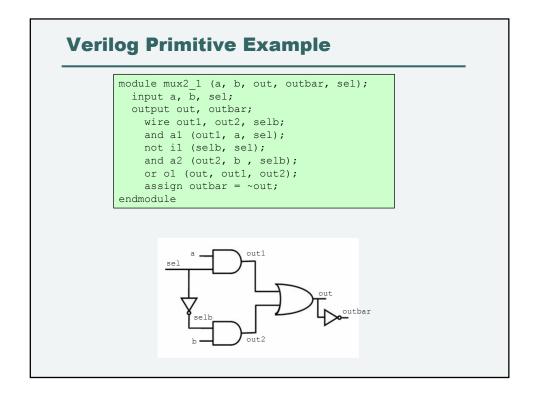

- Builtin primitives (NAND, NOR,...)

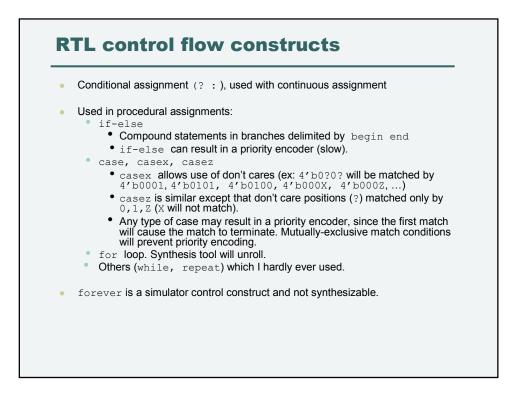

- Control Flow (if-else,...)

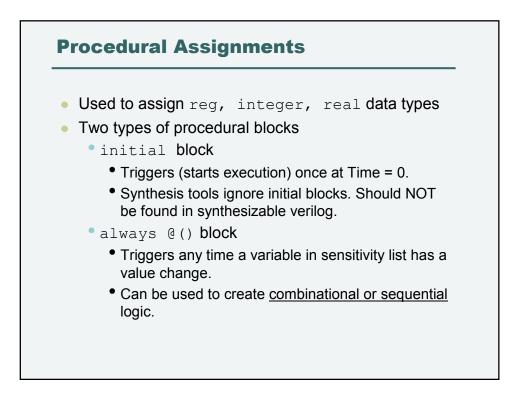

- Continuous and Procedural Assignments

- Behavioral coding vs coding for "synthesis"

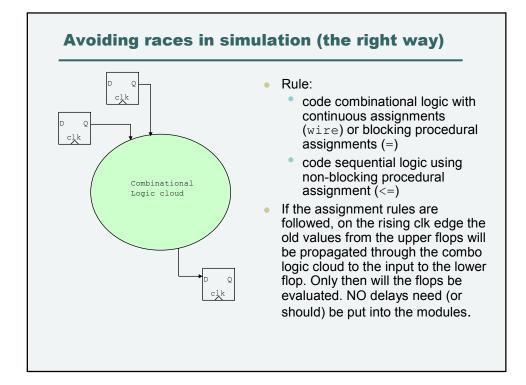

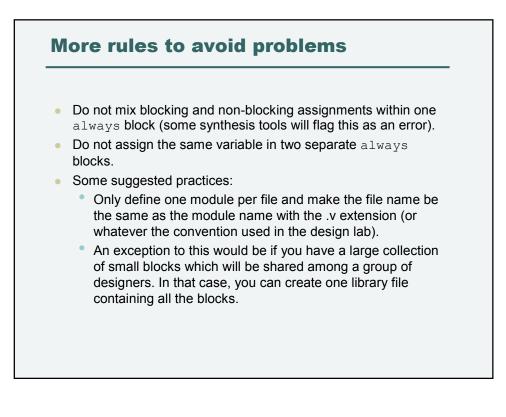

- Simulator behavior and avoiding problems

- Unintended latches

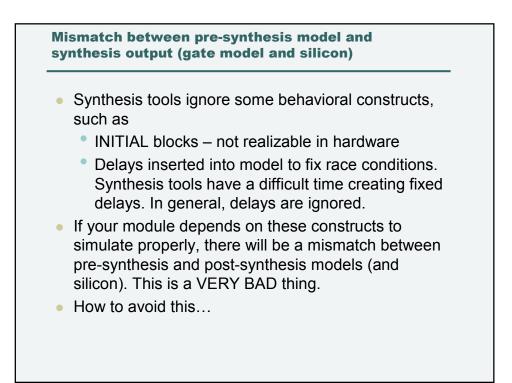

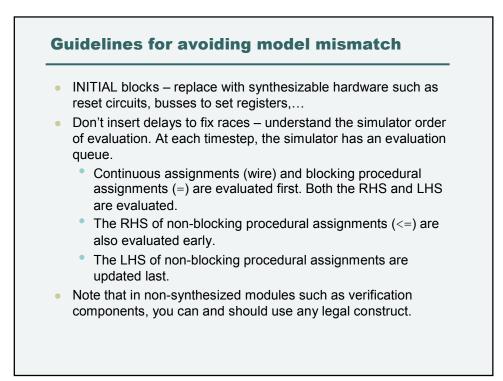

- How to avoid mismatch

- Some simple examples

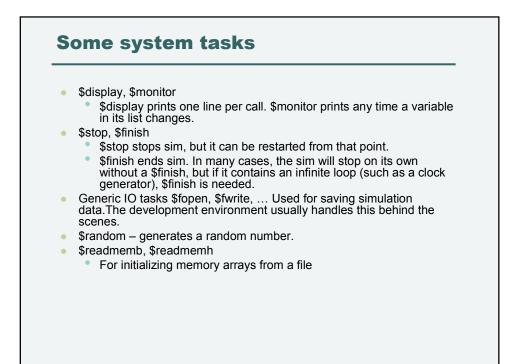

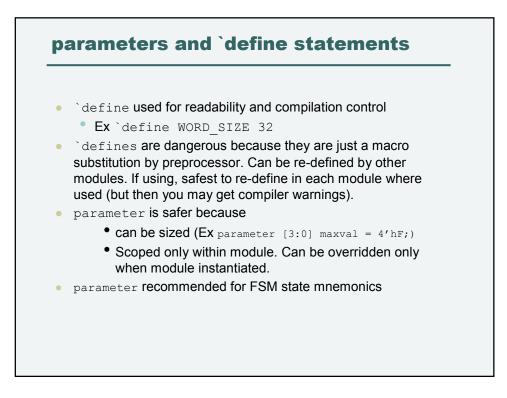

- Misc system tasks, parameters, defines

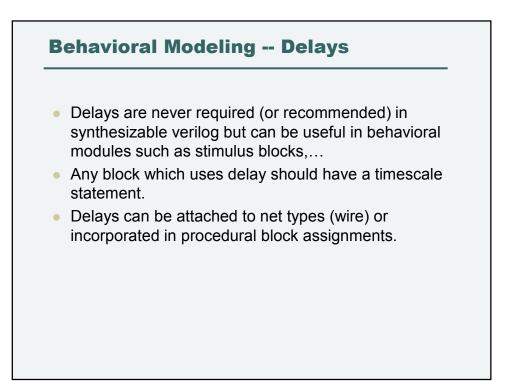

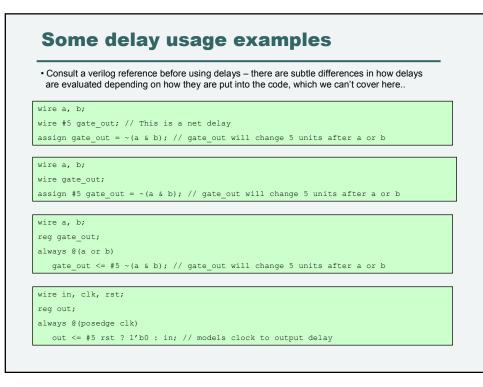

- Behavioral modelling delays

- FSM example

### Structure of a module module full adder(ci,a,b,sum,cout); // port declarations input a,b,ci; output sum, cout; // type declarations. wire a, b, ci, sum, cout; // assignments assign sum = a ^ b ^ ci; assign cout = (a & b) | (a & ci) | (b & ci); endmodule Syntax notes · Statements end with ; • Compound statements (see later) are delimited by begin end (like { } in C). • Port directionality and width declared. • Variable types must be declared, as in other programming languages.

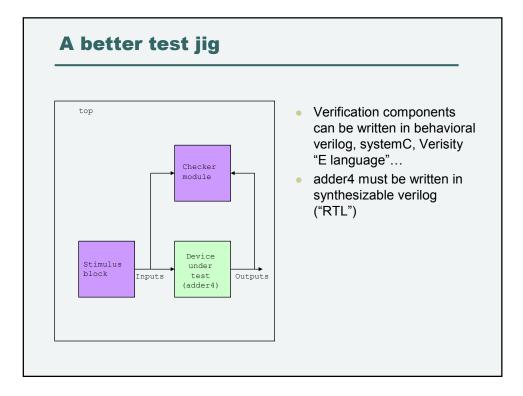

| odule top;             |                                                                             |

|------------------------|-----------------------------------------------------------------------------|

| wire [3:0] xa, xb, xsu | ım ;                                                                        |

| wire xci, xcou         | ıt;                                                                         |

| // Instantiate 4 bit a | adder                                                                       |

| adder4 my_adder(// Out |                                                                             |

|                        | <pre>sum(xsum[3:0]), .xcout(xcout),</pre>                                   |

|                        | Inputs                                                                      |

| . X                    | <pre>xa(xa[3:0]), .xb(xb[3:0]), .xci(xci));</pre>                           |

| // Instantiation check | ter                                                                         |

| check_adder my_checker |                                                                             |

|                        | .xa(xa[3:0]), .xb(xb[3:0]), .xci(xci),<br>.xsum(xsum[3:0]), .xcout(xcout)); |

| // Instantiate stimulu | is block                                                                    |

| stimulus my_stim(// Ou | itputs                                                                      |

|                        | xa (xa[3:0]),                                                               |

|                        | xb (xb[3:0]),                                                               |

|                        | xci(xci));                                                                  |

| dmodule // top         |                                                                             |

| Туре                   | Width of    | Symbol         | ]                                          |

|------------------------|-------------|----------------|--------------------------------------------|

| <b>7</b> 1 -           | Result      |                |                                            |

| Arithmetic             | >Ops width  | + - * / %      | 4'b0110 - 4'b0111<br>yields 5'b11111       |

| Logical                | 1 bit       | ! &&           |                                            |

| Bitwise                | Ops width   | ~ &   ^ ~^     |                                            |

| Relational             | 1 bit       | > < >= <=      |                                            |

| Equality               | 1 bit       | == != === !==  | Note: use ? for<br>don't cares             |

| Reduction              | 1 bit       | & ~&   ~  ^ ~^ |                                            |

| Shift                  | Ops width   | >> <<          | Note: vacant<br>positions zero-<br>filled. |

| Concatenate, replicate | > Ops width | {,,} {{}}      |                                            |

| Conditional            | Ops width   | ?:             |                                            |

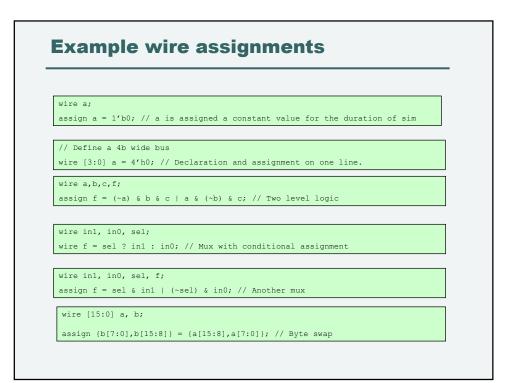

| <ul> <li>Used to represent</li> </ul>      |                                                                                                 |

|--------------------------------------------|-------------------------------------------------------------------------------------------------|

|                                            | connections between blocks                                                                      |

| -                                          | ue assigned in "continuous assignment" statement.<br>e can be of $reg$ (see below) or net type. |

| <ul> <li>wire is most community</li> </ul> | nonly used member of net class                                                                  |

| <ul> <li>Others are wand</li> </ul>        | , wor, tri, triand, trior, trireg.                                                              |

| <ul> <li>Used for combination</li> </ul>   | onal logic                                                                                      |

| <ul> <li>Limited conditional</li> </ul>    | assignment language features                                                                    |

| reg                                        |                                                                                                 |

|                                            | doesn't NECESSARILY imply a hardware register.                                                  |

| • •                                        | dural assignment" block.                                                                        |

| •                                          | e can be of reg or net type.                                                                    |

| •                                          | blocking" assignments (more on this later)                                                      |

| <ul> <li>Richer set of condi</li> </ul>    | tional assigments                                                                               |

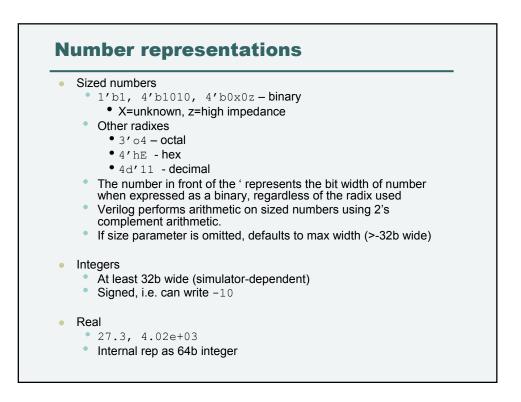

| real, realtime                             | umbers, but represented internally as 64b integers                                              |

| 0.1                                        | umbers, but represented internally as 64b integers                                              |

| <ul> <li>Supports scientific</li> </ul>    | as well as real (XXX.XX) notation<br>havioral modelling.                                        |

### Scope

Variables (wire, reg, ...) have local scope (within module). No global variables in verilog.

### **Hierarchical Reference to Signals**

- Signals down within a hierarchy can be referenced as:

- a.b.c.<sig\_name>

- where  $\mathtt{a}$  ,  $\mathtt{b}$  ,  $\mathtt{c}$  are module instance names and

- sig\_name = signal name

- Example: at the level of module top, internal signal cout\_int[1] within instance my\_adder of module adder4 can be referenced by my adder.cout int[1]

- Cannot assign (change) a signal thru hierarchical reference, only test. Would only be used in test.

# <section-header><section-header>

| Another way to accidentally infer a latch                                                                                                                     |                                                                  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| <ul> <li>Forgetting an item in the sensitivity list. <u>The always block only</u><br/><u>executes when an item in the sensitivity list changes</u></li> </ul> |                                                                  |  |

| mod                                                                                                                                                           | ule mux(ina, inb, inc, ind, sel, out);                           |  |

|                                                                                                                                                               | input [3:0] ina, inb, inc, ind;                                  |  |

|                                                                                                                                                               | input [1:0] sel;                                                 |  |

|                                                                                                                                                               | output [3:0] out;                                                |  |

|                                                                                                                                                               | wire [3:0] ina, inb, inc, ind;                                   |  |

|                                                                                                                                                               | wire [1:0] sel;                                                  |  |

|                                                                                                                                                               | reg [3:0] out;                                                   |  |

|                                                                                                                                                               | always @(ina or inb or inc or ind or sel)                        |  |

|                                                                                                                                                               | case (sel)                                                       |  |

|                                                                                                                                                               | 2'b00: out = ina;                                                |  |

|                                                                                                                                                               | 2'b01: out = inb;                                                |  |

|                                                                                                                                                               | 2'b10: out = inc;                                                |  |

|                                                                                                                                                               | 2'b11: out = ind; // This line will NOT execute when ind changes |  |

|                                                                                                                                                               | endcase // case(sel)                                             |  |

|                                                                                                                                                               | module // mux                                                    |  |

Since out is a reg type, it will hold its previous value when ind changes.

Because this is such a common error, later versions of verilog allow a shorthand notation always @ (\*) which will be filled in with the appropriate variables

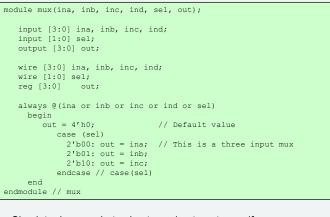

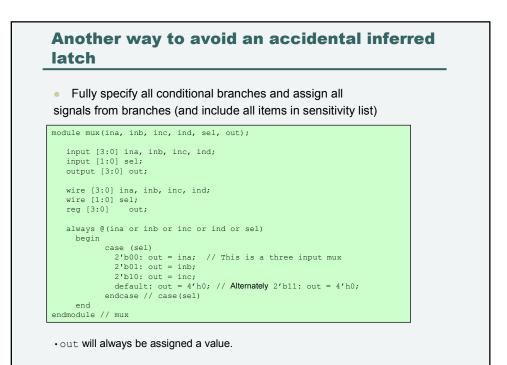

Precede all assignments with a default value (and include all items in the sensitivity list)

Simulator knows what value to assign to out even if no case condition is satisfied.

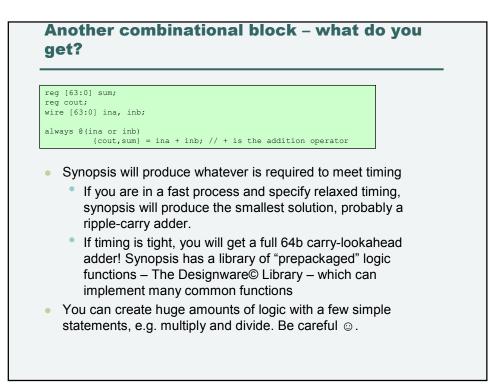

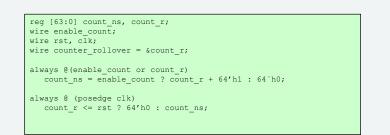

# Yet another combinational block – what do you get?

• This will produce a synchronous counter

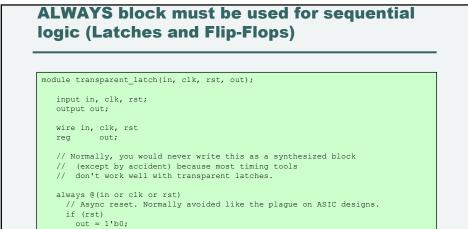

// must hold its value when clk is low and rst is not asserted

else if (clk)

out = in;

endmodule // transparent\_latch

// No else clause for this if => the latch

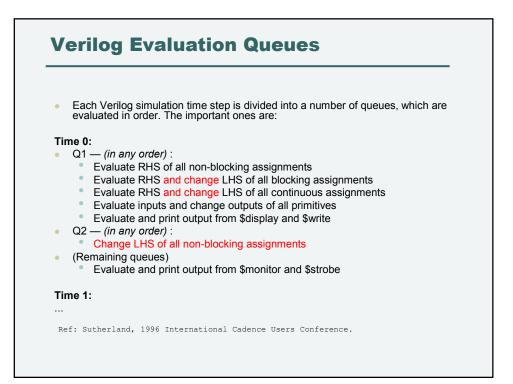

- = within procedural block is a blocking assignment

- Blocking assignments within an always block are completed in order, execute only after the previous statement is completed. If there is a delay in the previous statement (see later), the next statement will wait for the delay.

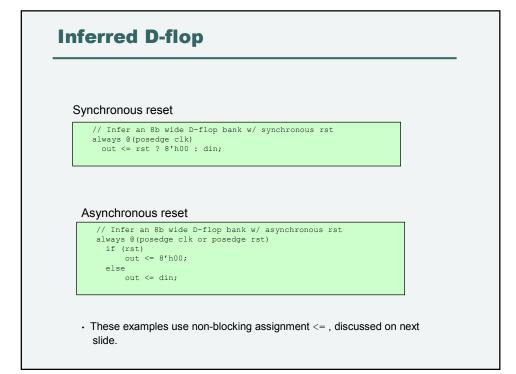

- <= within a procedural block is a non-blocking assignment. Non-blocking assignments do not wait for the previous statement to complete. They can be used to model concurrent operations.

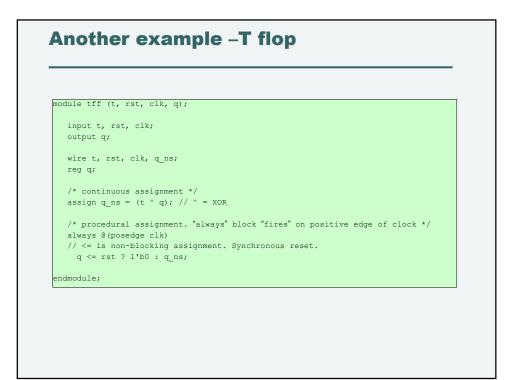

- RTL does not use delays. A more important distinction is the order the simulator evaluates these two assignments ...

# Simple example – D flop with load and synchronous reset

### module dff1 (d, ld, rst, clk, q);

input d, ld, rst, clk; output q; wire d, ld, rst, clk, q\_ns; reg q; /\* continuous assignment \*/ assign q\_ns = 1'b0; // WHAT GOES HERE?? /\* procedural assignment. "always" block "fires" on positive edge of clock \*/ always @(posedge clk)? // <= is non-blocking assignment. Synchronous reset. q <= rst ? 1'b0 : q\_ns; endmodule // dff1

| parameter example                                                                |  |

|----------------------------------------------------------------------------------|--|

| · · · ·                                                                          |  |

|                                                                                  |  |

|                                                                                  |  |

|                                                                                  |  |

|                                                                                  |  |

| <pre>module par_reg(q, d, clk, rst); parameter width = 8; // Default width</pre> |  |

| input [(width-1):0] d;                                                           |  |

| input clk, rst;                                                                  |  |

| output [(width-1):0] q;                                                          |  |

| reg [(width-1):0] d;                                                             |  |

| always @(posedge clk)                                                            |  |

| <pre>q &lt;= rst ? {width{1'b0}} : d;</pre>                                      |  |

| endmodule // par_reg                                                             |  |

|                                                                                  |  |

|                                                                                  |  |

|                                                                                  |  |

|                                                                                  |  |

|                                                                                  |  |

|                                                                                  |  |

|                                                                                  |  |

| dule test_par_reg;                   |                                                     |

|--------------------------------------|-----------------------------------------------------|

| reg [15:0] d;                        |                                                     |

| wire [15:0] g;                       |                                                     |

| wire clk, rst;                       |                                                     |

| // Instantiate a 16b reg             |                                                     |

| par reg #(.width(16))                |                                                     |

|                                      | -1):0]), .d(d[(width-1):0]), .clk(clk), .rst(rst)); |

| my_par_reg(.q(q)(wrach               | 1,.0]), .u(u[(widen 1).0]), .erk(erk), .ise(ise)),  |

| <pre>clk_gen cgen(.clk (clk));</pre> |                                                     |

| initial                              |                                                     |

| begin                                |                                                     |

| d=16'h0000;                          |                                                     |

| rst=1;                               |                                                     |

| #6 rst=0;                            |                                                     |

| d=16'h5555;                          |                                                     |

| #10                                  |                                                     |

| d=16'hAAAA;                          |                                                     |

| #10                                  |                                                     |

| d=16'hFF00;                          |                                                     |

| #10                                  |                                                     |

| d=16'h00FF;                          |                                                     |

| end // initial begin                 |                                                     |

| initial                              |                                                     |

|                                      | 0.1                                                 |

| \$display(\$time, " d=%h,            | q=%h",d,q);                                         |