GXSTEST is the utility program which tests the proper functioning of the XESS protoboard. The program interface is illustrated below. Simply select the type of protoboard, such as XSA-50, and the parallel port that the host computer is connected too via the parallel port cable. Finally, select the "TEST" pushbutton. This program downloads a test program onto the FPGA to test the functionality of the protoboard. A message will be displayed whether the test passed or an error message. For additional details, refer to the GSXtools User's Manual.

2. GXSLOAD

GXSLOAD is the utility program which downloads the bit file created as part of the FPGA design flow onto the FPGA. The program interface is illustrated below. Simply select the type of protoboard, such as XSA-50, and the parallel port that the host computer is connected too via the parallel port cable. Using Windows "My Computer", go to the directory where the bit file was created. Simply drag the *.bit file to the column FPGA/CPLD of the GSXload program. At this point the "LOAD" pushbutton will be highlighted. Press "LOAD" to download the program. A proper download can be observed by looking at the 7-Segment LED on the XSA-50 protoboard. If the "dot" on the lower right hand corner of the 7-Segement LED is illuminated, then the download was successful. In addition, files/programs can be downloaded to the RAM or EEPROM on the XSA-50. For additional details, refer to the GSXtools User's Manual.

GXSPORT is the utility program which permits input control to the FPGA via the parallel port. In effect this program acts as an 8-pin DIP switch. The program interface is illustrated below. Select the the parallel port that the host computer is connected too via the parallel port cable. And select the binary representation of the inputs and press "Strobe". Another feature is counting-up the binary inputs to the FPGA. To use this option, select the "Count" box. For additional details, refer to the GSXtools User's Manual.

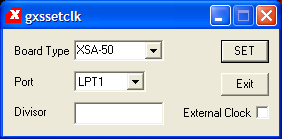

4. GXSSETCLK

GXSSETCLK is the utility program which programs the programmable clock. A divisor in the range from 1 to 2052 will permit the programmable clock to divide down the 100MHz clock by the divisor. In other words, the programmable clock has a range of 100MHz down to approximately 48.7KHz. If a slower clock rate is desired, other techniques must be employed. For additional details, refer to the GSXtools User's Manual.

Created by: David M. Sendek, July 2003