# ModelSim v5.7 Quick Reference Guide

Author: David M. Sendek

**Background:** This guide provides you with step-by-step procedures in using ModelSim to compile, link and simulate your VHDL or Verilog source code design. *These procedures provide you with the necessary steps to accomplish labs when using VHDL.*

### Assumptions:

- 1. Students have a basic understanding of UNIX

- 2. Students know how to sign-into a UNIX environment from Windows NT

References: (a) "Force File and Force Commands", David Sendek, 9 July 2003

- (b) ModelSim SE Tutorial Version 5.5e, 22 Aug 01, Mentor Graphics

- (c) Lesson 2 Basic VHDL Simulation, "Preparing the Simulation", Mentor Graphics, 22 Aug 01, pages T-18 to T-23

### **SETTING UNIX ENVIRONMENT** (steps at the UNIX prompt)

- 1. (Suggestion) Create a directory ee451

- 2. (Suggestion) Create a sub-directory for each lab, ex: lab1, lab2, ...

- 3. %setenv MGC WD \$HOME/path

- ex: %setenv MGC\_WD \$HOME/ee451/lab1

- 4. Change to your working lab sub-directory

- 5. %source /mentor/csu\_setup/ams\_setup.csu

Notes:

- This permits you to access ModelSim, used for compiling, linking and simulating VHDL source code.

- If you do not modify your .cshrc file, you must repeat steps 3 through 5 each time you re-open your UNIX window.

- There is a **space** between %source and /mentor....

#### **Procedures:**

- 1. Using your favorite text editor, create the Very High Speed Integrated Circuit (VHSIC) Hardware Description Language (VHDL) source code for your design and a separate file with "force" commands to be used in simulating your design (if required). The force file is a set of test vectors to test your design. Reference (a) provides some force commands. Name the file such as "lab1.do"

- 2. From your /ee451/lab1 directory and at the Unix Prompt, start Mentor Graphics ModelSim by entering the following at the Unix prompt: qhsim

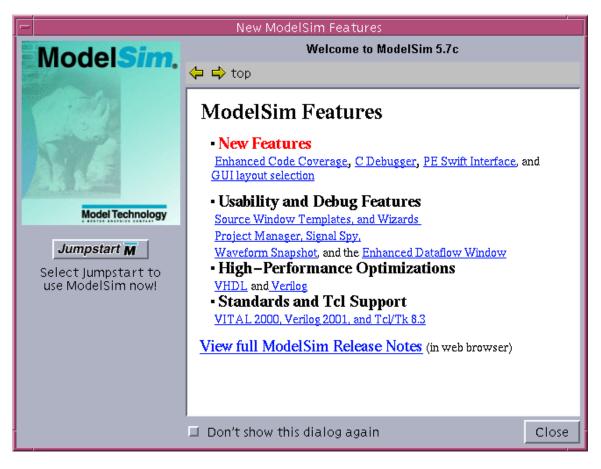

3. At the "Welcome to ModelSim 5.7" window, select "Jumpstart".

The following screen will be displayed. Select "Create a Project" or File > New > Project. Note: After you have initially created a project, future access to that project can be achieved by selecting "Open a Project".

The following will be displayed <u>if you have already created a project</u> and want to open it at some later time. This will add the files that contain your design. You can then directly proceed to compiling your design.

| F | - Open Project                                |

|---|-----------------------------------------------|

|   | Open Project                                  |

|   | m/home/vhdl/counter7segment/binary_up_counter |

|   | Browse                                        |

|   | OK Cancel                                     |

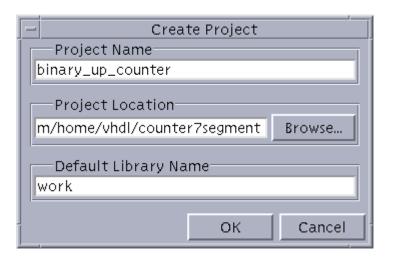

4. Before you compile any Hardware Design Language (HDL) (such as VHDL or Verilog), you'll need a design library to hold the compilation results. To create a new design library, type in the Project Name and select a directory where the project file will be stored. Leave the default library name set to "work". Finally, select OK.

After pressing OK, the following will be displayed:

| - | Add items to the             | Project           |

|---|------------------------------|-------------------|

| Г | —Click on the icon to add it | ems of that type: |

|   | ۲<br>Create New File Ac      | dd Existing File  |

|   | Create Simulation Cre        | ate New Folder    |

|   |                              | Close             |

And your ModelSim main window will look like the following:

|   |                                                                                                       | •            |

|---|-------------------------------------------------------------------------------------------------------|--------------|

| E | <u> E</u> ile <u>E</u> dit <u>V</u> iew <u>C</u> ompile <u>S</u> imulate <u>T</u> ools <u>W</u> indow | <u>H</u> elp |

|   | 🔓 🖻 🖀 🖉 🥩 🎬 🚑 🐹                                                                                       |              |

| ļ | Workspace                                                                                             |              |

| ŀ | Name Status Type Ord # // ModelSim SE Viewer 5.7c Mar 1<br>unOS 5.9<br># //                           | 2003 \$      |

|   | # // Copyright Model Technology, a<br>Graphics Corporation company, 2003                              | Mentor       |

|   | # // All Rig<br>served.                                                                               | hts Re       |

|   | # // UNPUBLISHED,<br>ED SOFTWARE.                                                                     |              |

|   | # // CONFIDENTIAL AND PROPRI<br>INFORMATION WHICH IS THE                                              |              |

|   | # // PROPERTY OF MENTOR GRAPH<br>RPORATION OR ITS LICENSORS.                                          | ICS CO       |

| ŀ | # //<br># Loading project binary_up_counter                                                           |              |

| ľ | Project Library                                                                                       |              |

| P | Project : binary_up_counter <a>No</a> No Context>                                                     | //,          |

5. The next step is to add the files that contain your design. By now you would have written your VHDL source code file(s). Click "Add Existing File" in the "Add items to the Project" window. For this example, three VHDL files are added. Click the "Browse" button in the "Add file to Project". It should be noted that counter7segment.vhd, counter.vhd & leddcd.vhd are selected. Select "Reference from current location" and then click OK. Close the "Add items to the Project" dialog (This will close the "Add items to the Project" and "ModelSim Jumpstart" windows).

| F | Add file to Project                                           |

|---|---------------------------------------------------------------|

| Г | File Name                                                     |

|   | /ECE/sendekdm/home/vhdl/counter7segment/leddcd.vhd Browse     |

|   | Add file as type Folder Top Level                             |

| • | Reference from current location 🛛 💠 Copy to project directory |

|   | OK Cancel                                                     |

The main ModelSim window will show the following:

| -                                                      | Мо                 | delSim SE       | VHDL 5.7c                                                                  | •            |

|--------------------------------------------------------|--------------------|-----------------|----------------------------------------------------------------------------|--------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>C</u> ompile | e <u>S</u> imulate | e <u>T</u> ools | Window <u>F</u>                                                            | <u>t</u> elp |

| 🖻 🖻 🛍 🕹 🕮 🚑 🕷                                          |                    |                 |                                                                            |              |

| Workspace                                              |                    | ×               |                                                                            |              |

| Name                                                   | Status Ty          | pe Oro          | ED SOFTWARE.<br># // CONFIDENTIAL AND PROPRIETARY                          | $ \Delta $   |

| 💾 counter7segment.vhd                                  | ? VH               |                 | INFORMATION WHICH IS THE                                                   |              |

| H counter.vhd                                          | ? VH               |                 | # // PROPERTY OF MENTOR GRAPHICS CO<br>RPORATION OR ITS LICENSORS.         |              |

| H leddcd.vhd                                           | ? VH               | DL 2            | # //                                                                       |              |

|                                                        | (                  | N               | # Loading project binary_up_counter<br># Loading project binary_up_counter |              |

|                                                        |                    |                 |                                                                            |              |

| Project Library                                        |                    |                 | ModelSim>                                                                  | $\mathbf{N}$ |

| Project : binary_up_counter                            | gn Loaded>         |                 | No Context>                                                                |              |

6. Now you are ready to compile the VHDL or Verilog file(s). To compile the file(s), select Compile > Compile All or highlight the "high-level" design (counter7segment.vhd in this example), right mouse click and select Compile > Compile All. By selecting the "Library" tab, you can observe the compiled design units (the Entity & Architecture blocks).

|                                        |                            |        | M             | odelSim SE                                        | VHDL 5.7c                                                                                           | •             |

|----------------------------------------|----------------------------|--------|---------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew | <u>C</u> ompile <u>S</u> i | mulate | <u>T</u> ools | <u>W</u> indow                                    |                                                                                                     | <u>H</u> elp  |

| 🛛 😅 🖻 🛍 🛛 🕸 🗄                          | 1 🚑 🕺                      |        |               |                                                   |                                                                                                     |               |

| Workspace ====                         |                            |        |               | <u>×</u>                                          | ( _ <del>= </del>                                                                                   |               |

| ime                                    | Status                     | Туре   | Order         | Modifie                                           | # // PROPERTY OF MENTOR GRAPHICS CORPORATION<br>OR ITS LICENSORS.                                   | $\Box \Delta$ |

| 📊 counter7segmen                       | it.vhd 🧹                   | VHDL   | 0             | 07/22/03                                          | # //                                                                                                |               |

| 🖬 counter.vhd                          |                            | VHDL   | 1             | 07/22/03                                          | # Loading project binary_up_counter                                                                 |               |

| 📊 leddcd.vhd                           | ×                          | VHDL   | 2             | 07/22/03                                          | <pre># Loading project binary_up_counter<br/># Compile of counter7seqment.vhd was successful.</pre> | - 110         |

|                                        |                            |        |               |                                                   | # Compile of counter.vhd was successful.                                                            |               |

|                                        |                            |        |               | $\vdash$                                          | # Compile of leddcd.vhd was successful. # 3 compiles. 0 failed with no errors.                      |               |

| Project Library                        | <u>ا</u>                   |        |               |                                                   | ModelSime                                                                                           | $\nabla$      |

| Project : binary_up_counte             | er 🛛 < No Design Loa       | ded>   |               | <no conte<="" th=""><th>xt&gt;</th><th></th></no> | xt>                                                                                                 |               |

| Mod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | delSim SE VHDL 5.7c 🛛 🔤                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>C</u> ompile <u>S</u> imulate <u>T</u> ools <u>V</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u>√</u> indow <u>H</u> elp                                                                    |

| 🔁 🖻 🖺 🔌 🕮 🚑 🐹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                |

| Workspace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                |

| Name     Type     Path       Image: Straight of the s | nts/( # // UNPUBLISHED, LICENSED SOFTWAR<br>E.<br># // CONFIDENTIAL AND PROPRIETARY INFORMATIO |

| Eleddcd Entity /top/stude     Architecture     Project] Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <pre>nts/(</pre>                                                                               |

| Project : binary_up_counter No Design Loaded>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <no context=""></no>                                                                           |

- 7. You may find compile errors in the previous step. These need to be corrected before proceeding any further.

- 8. Now the design must be loaded, once compiled. Double-click the "high-level" design (counter7segment) on the Library page. You'll see a new page appear in the workspace that displays the structure of the counter7segment design unit.

| ModelSim SE V                                                                                  | /HDL 5.7c 🛛 🕴                                                                                                                                                              |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>C</u> ompile <u>S</u> imulate <u>T</u> ools <u>V</u> | <u>M</u> indow <u>H</u> elp                                                                                                                                                |

| 🔁 🛍 🕄 🤣 🔛 🚑 🐹 🛛 EF 100 fs 🕏 EL EL                                                              | ±↓ 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                   |

| Workspace 🔤 🖬                                                                                  |                                                                                                                                                                            |

| Instance Design Unit Design Unit Ty;<br>                                                       | vsim work.counter7segment<br># vsim work.counter7segment<br># Loading /mentor/AMS/modelsim/v5.7c/bin/.<br>./sunos5//std.standard                                           |

| ☐ ☐ leddcd1 leddcd(behArchitecture<br>☐ std_logistd_logicPackage                               | <pre># Loading /mentor/AMS/modelsim/v5.7c/bin/.<br/>./sunos5//ieee.std_logic_1164(body)<br/># Loading /mentor/AMS/modelsim/v5.7c/bin/.</pre>                               |

| ばいたい 「「「「」」」」」」」」」」」」」」」」」」」」」」」」」」」」」」」」                                                      | <pre>./sunos5//ieee.std_logic_arith(body) # Loading /mentor/AMS/modelsim/v5.7c/bin//sunos5//ieee.std_logic_unsigned(body) # Loading work.counter7segment(structural)</pre> |

| Project Library sim Files                                                                      | <pre># Loading work.counter(behavioral) # Loading work.leddcd(behavioral) VSIM 5&gt;  </pre>                                                                               |

| Project : binary_up_counter Now: 0 fs Delta: 0                                                 | sim/:counter7segment                                                                                                                                                       |

9. To simulate the design, select View > All Windows from the main ModelSim window. This will open all the ModelSim simulation windows, such as the wave window. This window will be what you will predominately use.

| ModelSim SE VHDL 5.7c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | source – counter7segment.vhd 🔹 🗆                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Eile E</u> dit <u>V</u> iew <u>C</u> ompile <u>S</u> imulate <u>T</u> ools <u>W</u> indow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Help File Edit View Tools Window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Image: Standard Standard Package         Image | Image: Second |

| # .source .process .signales .dataflow .list .wave         Project Library sim Files         VSIM 6>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | als .variab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Project : binary_up_counter Now: 0 fs Delta: 0 sim/:counter7segment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| dataflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | sim/counter7segment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>N</u> avigate T <u>r</u> ace <u>T</u> ools <u>W</u> indow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>Insert Format T</u> ools <u>W</u> indow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Ø   N □ ⊕   X ▷ □ 2 ○ M   J + 4 + > > + + +  <br>Ø Ø Ø 0   0 0 0   10 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ☞ ■ ●   ½ ʰ ʰ ħ   \ X ½ ± 1   \ <u>□</u>   Q Q Q <b>K</b>   ¥   ¥   ↓<br>¥ ¥ X   3+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Welcome to the Enhanced Dataflow Window!<br>WARNING: No extended dataflow License exists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Now         0 fs         500         1           Cursor 1         0 fs         0 fs         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

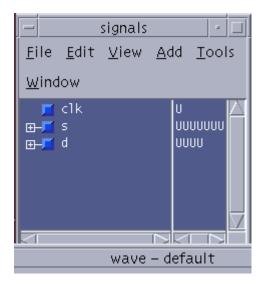

10. From the Signals window menu, select Add > Wave > Signals in Region. This command displays the top-level signals to the Wave window.

This will result in the following:

| -                                                      | wave – default                                   |     |

|--------------------------------------------------------|--------------------------------------------------|-----|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>I</u> nse    | ert F <u>o</u> rmat <u>T</u> ools <u>W</u> indow |     |

| 📂 🖬 🎒   🐰 🖻 🛍<br>11 14 24   3+                         | ) MA   _k 🕺 TE I   N 💽   @, Q, Q, 🗮   EF   E.    | Į   |

| ☐ :counter7seg<br>⊞—☐ :counter7seg<br>⊞—☐ :counter7seg | 000000                                           | Z   |

| Now                                                    | 0 fs ) 500 1                                     |     |

| Cursor 1                                               | 0 fs 0 fs                                        |     |

|                                                        |                                                  |     |

| 0 fs to 1 ps                                           |                                                  | 11. |

- 11. Of particular interest, if you are using a hierarchical design, the previous step only show the top-level signals. But if you require more detailed resolution, you can select from the signals window Add > Wave > Signals in Design.

- 12. Now you are ready to simulate your design. To simulate your design, you will use your test vectors that you placed in your force file. To execute your force file, to simulate your design, select Tools > Execute Macro from the main window menu. Finally, select the force file you created earlier. Note that a "force file" is also referred to as a "do" file.

| - |                     | Execute Do File                                          |                |

|---|---------------------|----------------------------------------------------------|----------------|

| D | irectory: 📝         | top/students/GRAD/ECE/sendekdm/home/vhdl/counter7segment | - È            |

|   | ] work<br>] test.do |                                                          |                |

|   |                     |                                                          |                |

|   |                     |                                                          |                |

|   |                     |                                                          |                |

| E | 1                   |                                                          |                |

|   | File <u>n</u> a     | ame: test.do                                             | <u>O</u> pen   |

|   | Files of <u>t</u>   | type: Macro Files (*.do,*.tcl)                           | <u>C</u> ancel |

A sample simulation may look like:

| -                                                     | wave – default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>I</u> nsert | F <u>o</u> rmat <u>T</u> ools <u>W</u> indow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| S ■ ④   X □ □ ■ ▲   S □ ↓ ■ ▲   X   3+                | 📐 💥 🗠 🛨   🔪 🖳   🍳 🤍 🌉   👫   🗄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u>.</u> |

| <pre>:counter7segment:clk</pre>                       | 0       1110111       1110111       1110111         1       1110111       1110111       1       1         1       1       1       1       1       1       1       1         1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 | X        |

| Now                                                   | 00000 fs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| Cursor 1                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 199518 fs to 199582 fs                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

- 13. To exit ModelSim, select File > Quit in the main ModelSim window.

- 14. After simulation, you can use the XESS Field Programmable Gate Array (FPGA) protoboard to verify your design on physical hardware.

## **Useful Feature(s):**

1. If you desire to clear your "wave" window during simulation, simply press the restart icon illustrated below.